IFMIP037 Main Menu

# World Automation Congress Third International Forum on Multimedia & Image Processing

Orlando, Florida, USA June 9-13, 2002

**Analog Integrate-And-Fire Neurochips: Neural Competition In Frequency And Time Domains**

Tetsuya Asai, Hideki Hayashi, And Yoshihito Amemiya

# Analog Integrate-and-Fire Neurochips: Neural Competition in Frequency and Time Domains

Tetsuya Asai, Hideki Hayashi, and Yoshihito Amemiya

Department of Electrical Engineering, Hokkaido University, Kita 13, Nishi 8, Kita-ku, Sapporo, 060-8628, Japan.

#### Abstract

In this report, we present an inhibitory neural network, implemented on analog CMOS chips, that exhibits competitive behaviors in the frequency and time domains. The circuit for each neuron was designed to produce sequences in time of identically-shaped pulses, called *spikes*. The result of experiment and simulation revealed that the network more efficiently achieved the selective activation and inactivation of the neuron circuits on the basis of spike timing rather than of firing rates. The results indicate that the spike-timing-based neural processing by spiking neuron circuits provides a possible way of overcoming low tolerance problems of analog devices in noisy environments.

# **Keywords**

Analog VLSI, Competitive neural network, Spike-timing code, Integrate-and-fire neurons.

#### I. Introduction

Silicon circuits that mimic the nervous systems of insects and other animals represent the future of neurocomputing [1]. The merit of mimicking a nervous system is that artificial neural systems that include various neural functions can naturally be created by reconstructing the microstructures of a nervous system (neural network) on a silicon chip. Analog VLSI is a key to the implementation of large-scale neural networks. However, traditional models of neurons and neural networks are not suitable for analog VLSI implementation due to the requirement for accuracy in a computation; i.e., analog devices have poor properties in terms of the matching and temperature dependence of device characteristics and have a low degree of tolerance to noisy environments. Therefore it is essential to resolve the lack of precision and reproducibility at the device level by introducing redundancy at the hardware neural-network level.

Although the precision, reliability, and noise properties available in single neuron fall short of those used in even the most rudimentary analog VLSIs, the nervous system exhibits marvelously accurate behavior. For example, echolocating bats are apparently able to resolve jitter in the arrival time of their echoes with a precision of 10 nanoseconds [2]. Recent physiological and theoretical studies support the possibility that accurate spike timing has a role in cortical processing [3]; e.g., constant stimuli lead to imprecise spike trains, whereas stimuli that include fluctuations produce spike trains with timing that is reproduced within 1 milliseconds [4]. The results indicate that a low level of intrinsic noise in spike generation allows cortical neurons to accurately transform a synaptic input into a sequence of spikes.

Fukai showed that a network of inhibitory integrate-and-fire neurons (IFNs) achieves a robust and efficient neural competition on the basis of a novel timing mechanism of neural activity [5]. We found that the network with such timing mechanism provides an appropriate basis for the development of analog VLSI circuits that overcome the problem of analog devices, namely the lack of precision and reproducibility. In this report, we present a novel analog IFN circuit that can easily be implemented on analog VLSIs. We show,

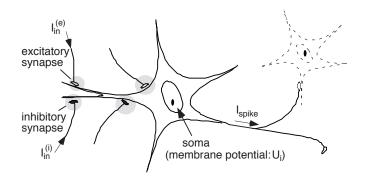

Fig. 1. Schematic image of the neuron model.

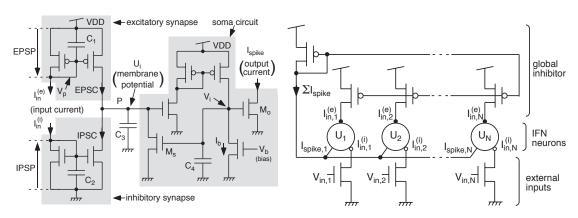

Fig. 2. The IFN circuit.

Fig. 3. Inhibitory neural circuits using IFNs.

by both experiments and computer simulations, that a network of the IFN circuits very efficiently achieves a robust form of neural competition that is based on spike timing rather than firing rates.

# II. THE IFN AND NETWORK CIRCUIT

Figure 1 is a schematic image of a neuron model. The neuron accepts input currents,  $I_{\text{in}}^{(e)}$  and  $I_{\text{in}}^{(i)}$ , through the excitatory and inhibitory synapses, respectively. The membrane potential  $U_i$  is produced at the soma as the result of the integration of the input currents. An excitatory input increases the membrane potential, whereas an inhibitory input decreases the potential. When the potential exceeds a threshold value, the neuron produces a current pulse  $I_{\text{spike}}$  and the membrane potential is reset to its resting value. This model of the neuron is called the integrate-and-fire neuron (IFN) [6].

Figure 2 shows an IFN circuit constructed of analog CMOS circuits. The circuit implements the excitatory and inhibitory synapses of the neuron model as well as the soma. The excitatory input current  $I_{\rm in}^{(e)}$  produces the excitatory postsynaptic potential (EPSP) in the excitatory synapse circuit. The membrane potential  $U_i$  is thus increased by the excitatory postsynaptic current (EPSC) that is produced by the EPSP. Similarly, the inhibitory input  $I_{\rm in}^{(i)}$  decreases the membrane potential through the inhibitory postsynaptic current (IPSC) that is produced by the inhibitory postsynaptic potential (IPSP). An increase in the membrane potential induces an increase in potential  $V_i$ . Thus, when the membrane potential exceeds a certain threshold voltage, input node P of the membrane is suddenly shunted by

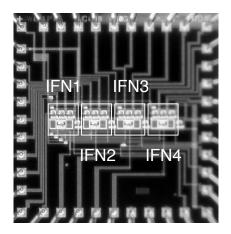

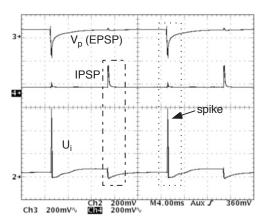

Fig. 4. Micrograph of the fabricated IFN chip. Fig. 5. Experimental results for a IFN circuit

transistor  $M_s$ . The shunted current increases exponentially with the membrane potential. This sudden increase in the current represents the spike generation. The output current  $I_{\text{spike}}$  is obtained by transistor  $M_o$ .

The input current  $I_{\rm in}$  and bias current  $I_b$  for the circuit determine the magnitude of the spike and the duration of the refractory period. If both the input current and the bias current are less than 100 nA, the MOS transistors of the IFN circuit operate in their subthreshold region [7], where the IFN circuit consumes very little power (on the order of nW or less) but the MOS transistors are very sensitive to external noise. We are interested in whether or not the IFN network is able to overcome the noise sensitivity.

We constructed an inhibitory neural network in which the IFN circuits are coupled to each other through all-to-all inhibitory connections of equal strength. This reduces the complexity of the connection of N neurons to O(N). Figure 3 shows the reduced network consisting of N IFN circuits and a global inhibitor constructed of (N+1) pMOS transistors. Each IFN circuit accepts an intrinsic external input  $V_{\rm in}$ . The nMOS transistors connected to the IFN circuits produce an excitatory input current  $I_{\rm in}^{(e)}$ . The global inhibitor receives the sum of the IFN outputs  $(\sum_i^N I_{\rm spike,i})$ . This total current is copied in each IFN circuit to produce the inhibitory input current  $I_{\rm in}^{(i)}$ .

## III. Results

We fabricated a prototype IFN chip, using a 1.5  $\mu$ m CMOS process (MOSIS, vendor: AMI). Figure 4 is a photograph of the chip that contains four IFN circuits and one global inhibitor circuit. The capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  were designed with a large capacitance due to the limit on the time resolution of our measurement systems. The capacitors took up a total area of 120  $\mu$ m  $\times$  200  $\mu$ m.

Figure 5 shows experimental results for the fabricated IFN circuit. The supply voltage was set at 5 V and the bias current  $I_b$  was set at 100 nA. In the experiment, periodic current pulses were applied to the excitatory and inhibitory synapse circuit. When an input pulse was applied to the inhibitory synapse circuit, the membrane potential  $U_i$  was decreased by the increase in the IPSP (see box outlined by dashes in Fig. 5). Similarly, the membrane potential was increased by the input pulse applied to the excitatory synapse circuit. When the IPSP fell below a certain threshold voltage, a spike was generated (box outlined by dots in Fig. 5) because of the reduction of the shunting inhibition by the IPSC. The spike current  $I_{\rm spike}$  ( $\approx 100$  nA) was five orders of magnitude larger than the resting current ( $\approx 1$

Fig. 6. Experimental results for the four-IFN network.

pA), and these two are thus very easily distinguished from each other.

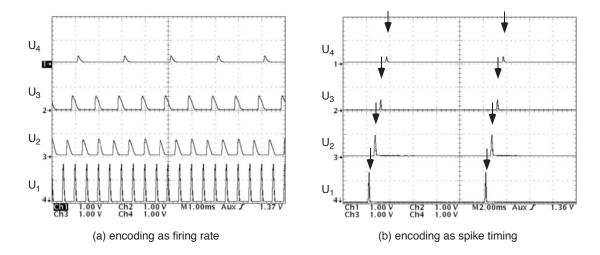

Figure 6 shows experimental results for a four-neuron network. In these experiments, external input values were encoded as either firing rate or spike timing. Encoding of the external input as a firing rate means that the strength of the external input is equivalent to the frequency of the train of identically-shaped voltage pulses  $V_{\rm in}$ . Encoding of the external input as spike timing code means that the strength is equivalent to the timing of spike generation relative to the timing of its external periodic input.

The results for a firing-rate encoded input are shown in Fig. 6(a). The amplitudes of the input current pulses  $|I_{\rm in}^{(e)}|$  were fixed at 100 nA. The frequencies of four periodic pulses  $I_{\rm in,1}^{(e)}$ ,  $I_{\rm in,2}^{(e)}$ ,  $I_{\rm in,3}^{(e)}$ , and  $I_{\rm in,4}^{(e)}$  were set at 200 kHz, 150 kHz, 100 kHz, and 50 kHz, respectively. Because an IFN circuit inhibits each other through the global inhibitor, an IFN receiving high-frequency input remained active, while those receiving low-frequency inputs became inactive.

When inputs encoded as spike timings were applied to the same network, the network exhibited a qualitatively quite different behavior, as shown in Fig. 6(b). Here, the external input values are transformed into the initial delay times of the periodic input pulses. In Fig. 6(b), the arrows show the timing at which each IFN received the input pulse. From this, it can be seen that competition occurred in terms of the times at which the input pulse reached the individual IFNs. This phenomena ("early arrival matters!") simply comes from the refractory period of the IFN circuits and lateral inhibition.

The next area of interest was the behavior of a large-scale IFN network in terms of overcoming the problem of the noise tolerance. It is rather difficult to construct a large-scale network of our prototype chips, because each chip includes only four IFN circuits. Therefore, we conducted SPICE simulations of a large-scale network, using device parameters obtained from the chip we fabricated.

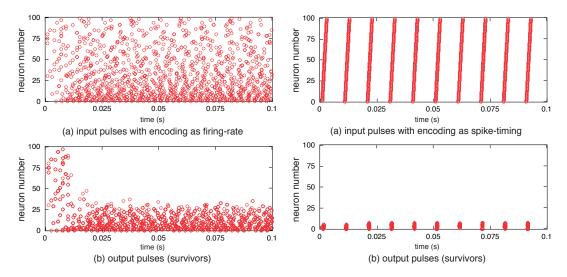

Figure 7 shows typical results obtained from the simulation of a 100-IFN network with firing-rate encoding. In the figure, the IFNs are represented by the neuron number labeled from 0 to 99. Each neuron receives input pulses with an amplitude of 10 nA at a timing represented by the circles in Fig. 7(a). The bias current  $I_b$  was set at 1 nA, while capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  were set at 1 pF, 10 pF, 10 pF, and 1 pF, respectively. Each circle in Fig. 7(b) represents the timing at which the *i*-th IFN circuit generated a spiking output

Fig. 7. Results of simulation of a 100-IFN Fig. 8. Results of simulation of a 100-IFN network (firing-rate encoding).

Fig. 9. Results of simulation of a 100-IFN network with noise (spike-timing encoding).

$I_{\text{spike}}$  of amplitude greater than 4.5 nA. As expected, those IFNs receiving high-frequency inputs remained active, while those receiving low-frequency inputs became inactive.

The reaction of the same network to spike timing was also simulated. Figure 8(a) shows the inputs with encoding as the spike timing. Those IFNs labeled by small numbers receive early input pulses, while those IFNs labeled with large numbers receive later input pulses. In this experiment, the first seven IFN circuits exhibited steady periodic responses, as is visible in Fig. 8(b).

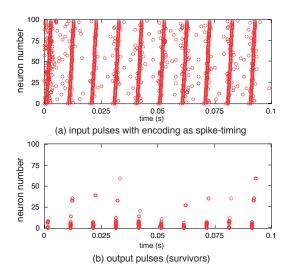

Figure 9 shows the result of a simulations in which the same network as was used to produce Fig. 8 was exposed to a noisy periodic input. The amplitude of the noise was set at 2 nA and its frequency was set at from one half to one-sixth of the periodic input. Six of the seven survivors shown in Fig. 8 ceased to exhibit a steady periodic responses, while some of the losers in the process of competition fired occasionally. Only the first survivor showed a steady periodic response to the input. When the amplitude of the noise was set

at 1 nA, the seven neurons that had survived in Fig. 8 exhibited steady periodic responses, while none of the losers fired. Although the amplitude of the noise is close to the order of the amplitude of the periodic input, the noise did not affect the activity of survivors that were distant from the border of losers. That is, an IFN receiving an input pulse earlier in each oscillatory cycle had a higher probability of firing than one receiving a pulse later in each oscillatory cycle. This implies that noise does *not* affect the essential features of the timing mechanism.

# IV. Summary

We have proposed and fabricated a simple integrate-and-fire neuron (IFN) circuit and an inhibitory neural network consisting of a small number of IFN circuits. The IFN circuit is designed to produce sequences of spikes in time according to the strengths of the signals on its inhibitory and excitatory inputs. Results of experiment and simulation revealed that the IFN circuits of the network exhibited competitive behavior in the frequency and time domains. The frequency-domain competition was achieved by introducing analog inputs that carried encoding in the form of the frequency of the firing rate, while competition in the time domain was achieved by having inputs that carried encoding in the form of the timing of spikes.

In the case of spike-timing encoding, an IFN circuit becomes a loser if it remains inactive or ceases to fire within several oscillatory cycles of the onset of the train of input pulses. Survivors exhibit steady periodic responses, while losers exhibit no activity. The distinction between survivors and losers is thus obvious from the spiking activity in time of the IFNs.

In the case of firing-rate encoding, however, the distinction is not very obvious from the activity in time. To determine the precise result of selection for activity or inactivity, mean firing rates of activities must be recovered a sufficiently long time. If a short time interval is used for averaging, the obtained firing rates do not reflect the relative intensity of the stimuli. Thus the responses of survivors do not, in general, represent the precise order of the stimuli. These observations lead us to conclude that the interpretation of the results is immediate and clear for spike-timing encoding, but is time-consuming and ambiguous in the case of a firing-rate encoding.

# ACKNOWLEDGEMENT

This study was supported by the "Analog Reaction-Diffusion Chip: The Development of Functional LSIs recovering Fingerprint Images" in '00 from the New Energy and Industrial Technology Development Organization (NEDO) of Japan.

### References

- [1] T. S. Lande Ed, Neuromorphic systems engineering: Neural networks in silicon. Kluwer Academic Publishers, USA, 1998.

- [2] A. J. Simmons, "A view of the world through the bat's ear: The formation of acoustic images in echolocation," *Cognition*, vol. 33, pp. 155-199, 1989.

- [3] F. Rieke, D. Warland, R. Steveninck, and W. Bialek, *Spikes: exploring the neural code*. MIT Press, Cambridge, 1989.

- [4] Z. F. Mainen and T. J. Sejnowski, "Reliability of spike timing in neocortical neurons," Science, vol. 268, pp. 1503-1506, 1995.

- [5] T. Fukai, "Competition in the temporal domain among neural activities phase-locked to subthreshold oscillations," *Biol. Cybern.*, vol. 75, pp. 453-461, 1996.

- [6] H. Tuckwell, Introduction to Theoretical Neurobiology, Cambridge Univ. Press, Cambridge, 1988.

- [7] E. A. Vittoz, "Micropower techniques," in *Design of MOS VLSI Circuits for Telecommunications*, Y. Tsividis and P.Antognetti, Eds., Prentice-Hall, NJ:Englewood Cliffs, 1985, pp. 104-144.