# A PTAT Voltage Source consisting of Subthreshold MOSFETs for Temperature Sensor LSIs

Ken Ueno, Tetsuya Asai, and Yoshihito Amemiya Department of Electrical Engineering, Hokkaido University, Sapporo 060-0814 Japan Tel: +81-11-706-7149, Fax: +81-11-706-7890 E-mail: k\_ueno@sapiens-ei.eng.hokudai.ac.jp

Abstract - An ultra-low power temperature sensor circuit based on a subthreshold MOSFET was proposed. The sensor consists of a modified  $\beta$ -multiplier self biasing circuit that uses a switched capacitor resistor instead of ordinary resistors. The circuit is operated in the subthreshold region, and it generates a proportional to absolute temperature (PTAT) voltage. Simulation with SPICE demonstrated that the circuit can be used as a smart temperature sensor with ultra-low power consumption of 3.5  $\mu$ W or less. The accuracy of the sensor output was within  $\pm 1.5^{\circ}$ C. Keywords: CMOS, Temperature sensor, PTAT, Subthreshold, Ultralow power

### I. INTRODUCTION

An ultra-low power LSIs have been required for low-cost and low-power LSI applications such as implantable medical devices, sensor networks, and portable mobile devices. In this paper, we propose one such sensor IC, a temperature sensor that can operate with a low power of microwatts or less. Many temperature sensors consisting of CMOS circuits have been reported [1],[2] but are unsuitable for use in ultra-low power systems because of their large power consumption of several hundred microwatts. To achieve ultralow-power operation, we propose a temperature sensor IC that uses MOSFET circuits operated in the subthreshold region. Our sensor produces an output voltage that is proportional to absolute temperature (PTAT).

# II. CIRCUIT CONFIGURATION

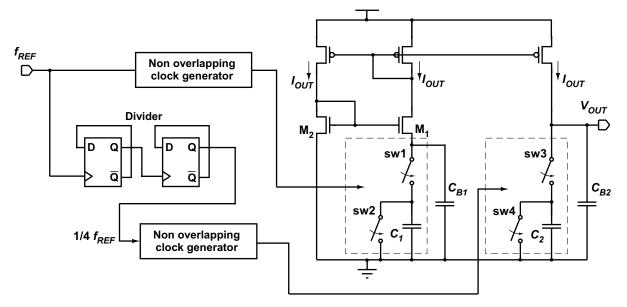

Figure 1 shows our PTAT voltage source. The circuit consists of a  $\beta$ -multiplier self biasing circuit, switched-capacitor resistors, a digital divider based on digital counters, and nonoverlapping circuits. Transistors M<sub>1</sub> and M<sub>2</sub> are operated in the subthreshold region. Capacitors  $C_{B1}$  and  $C_{B2}$  remove high-frequency noise caused by switching operation. The following describe the operation of the generator in detail.

The subthreshold MOS current  $I_D$  can be expressed as

$$I_D = K I_0 \exp\left(\frac{V_{GS} - V_{TH}}{\eta V_T}\right),\tag{1}$$

where K is the aspect ratio (=W/L) of transistors,  $I_0 (= \beta(\eta - \beta))$  $(1)V_T^2)$  is the process-dependent parameter,  $V_T(=k_BT/q)$  is the thermal voltage,  $V_{TH}$  is the threshold voltage of a MOSFET, and  $\eta$  is the subthreshold slope factor [3]. In the circuit in Fig.1, the current flowing in the circuit  $I_{OUT}$  is determined by the ratio of  $\mathrm{M}_1$  and  $\mathrm{M}_2$  and the resistance of switchedcapacitor resistor  $(f_{REF} \cdot C_1)^{-1}$ , and is given by

$$I_{OUT} = f_{REF} \cdot C_1 \cdot \frac{\eta k_B T}{q} \ln(K_2/K_1).$$

<sup>(2)</sup>

The voltage generator accepts the current  $I_{OUT}$  and the reference clock  $(1/4 \cdot f_{REF})$  with the digital divider, and is given by

$$V_{OUT} = 4 \cdot \frac{C_1}{C_2} \cdot \frac{\eta k_B T}{q} \ln(K_2/K_1).$$

(3)

Therefore, adjusting the capacitor ratio  $(C_1/C_2)$  and the number of digital counter, we can obtain the PTAT voltage with large temperature coefficient. The output voltage is insensitive to the process variations of capacitors because the output voltage depends on the capacitor ratio.

## **III. RESULTS**

We confirmed the operation of our circuit with the aid of SPICE simulation. We used the SPECTRE level 53 model with a parameter set for the 0.35- $\mu$ m 2P4M standard CMOS process. The supply voltage was set to 3 V, and the reference clock was set to 1 MHz.

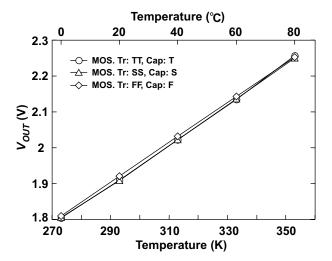

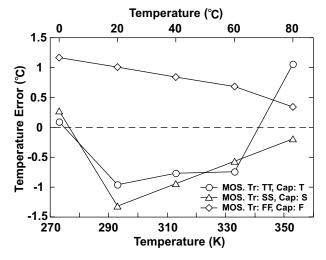

To verify the stability of the circuit operation in device variation, we performed a corner analysis, using parameters provided by the manufacturer. The worst corners of nMOS and pMOS transistors, and capacitors (S: slow, T: typical, and F: fast) were taken into consideration.

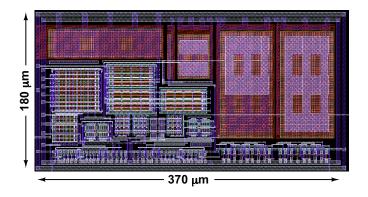

Figure 2 shows the output voltage  $V_{OUT}$  for for three different process corner conditions as a function of temperature in a range from 0°C to 80°C. As expected from Eq. (3), the value of  $V_{OUT}$  increased linearly with temperature. The average temperature coefficient of the three different corners was 5.5 mV/°C. The voltage error of difference between the simulation results and the theoretical results is shown in Fig. 3. The error shows a small value within  $\pm 1.5^{\circ}$  in a temperature range of 0°C to 80°C. Figure 4 shows a layout pattern of the sensor circuit. The area was  $0.07 \text{ mm}^2$ .

Table I summarizes the performance of our circuit. The power consumption was about 10  $\mu$ W at a 3-V supply voltage. Our circuit would be useful for smart temperature-sensor LSIs that are required to operate with ultra-low-power consumption.

#### REFERENCES

- [1] M. Pertijs, K. Makinwa, J. H. Huijsing, "A CMOS smart temperature sensor with a  $3\sigma$  inaccuracy of  $\pm 0.1$ °C from -55°C to 125°C," IEEE JSSC, pp. 2805-2815, 2005.

- P. Chen et, al., "A Time-Domain SAR Smart Temperature Sensor with [2] -0.25 - +0.35°C Inaccuracy for On-chip Monitoring," Proc. of the 34th European Solid-State Circuits Conference, pp. 70-73, 2008.[3] Y. Taur, T.H. Ning, "Fundamentals of Modern VLSI Devices," Cambridge

- University Press, 2002.

Fig. 1: Circuit configuration of our PTAT voltage source.

Fig. 2: Simulated output voltage as a function of temperature.

Fig. 3: Calculated temperature error of output voltage without calibration and trimming techniques.

Fig. 4: Layout pattern of our circuit. Area is 0.07mm<sup>2</sup>.

| Process         | 0.35-μm CMOS         |

|-----------------|----------------------|

| Temp. range     | 0 - 80 °C            |

| V <sub>DD</sub> | 3 V                  |

| Supply current  | 3.5 μΑ               |

| T.C.            | 5.5 mV/ °C           |

| Temp. error     | ±1.5 °C              |

| Area            | 0.07 mm <sup>2</sup> |

Table I: Performance Summary