# Dynamic Logic Circuit with Chaotic Transition Using Switched-Capacitor Chaotic Neuron Circuits

Kazuyoshi Ishimura\* †, Jun Takahashi††, Yoshihiko Horio† and Kazuyuki Aihara‡

†Graduate School of Engineering, Tokyo Denki University, Chiyoda-ku, Tokyo, 101-8457 Japan ††Aihara Electrical Engineering Co. Ltd., 2-16-8, Hama-cho, Funabashi-shi, Chiba, 273-0012 Japan ‡Institute of Industrial Science, The University of Tokyo, Meguro-ku, Tokyo, 153-8505 Japan

Abstract—Complex responses, including chaotic responses, were observed through physiological experiments with biological neurons. To include these complex responses, the chaotic neuron model was proposed. Chaotic dynamical systems have been applied to logical systems, and to information and signal processing systems. In this paper, we propose a dynamic logic element with a chaotic transition region using the chaotic neuron model. Logic functions of the proposed element can be dynamically changed through external signals, allowing a single logic element to serve several logic functions. As an illustration, we implement an EXOR logic element with switchedcapacitor circuit techniques implementing chaotic transition responses. In the circuit implementation, we simplify the original 2-neuron circuit into a 1-neuron circuit by employing a simple nonlinear function circuit. From circuit experiments, we confirm the EXOR characteristics and chaotic transition regions of the proposed circuit.

# 1. Introduction

The McCulloch–Pitts neuron model approximates a real neuron through logical functions [1]. A network using this model can constitute any logic function with proper thresholds and coupling coefficients.

Chaotic and periodic responses have been observed through electrophysiological experiments with a squid giant axon, and using numerical analyses according to the Hodgkin–Huxley model [2]. The Hodgkin–Huxley model is important for research on high-level information processing in the brain. The Hodgkin–Huxley model is complex, however, and uses many parameters. Simulations and analyses are therefore difficult for large-scale neural networks consisting of Hodgkin–Huxley neurons.

In contrast, the chaotic neuron model proposed in [3] qualitatively represents the chaotic responses of real neurons. In other areas, too, research on chaos-based information and signal processing is a very active field [4, 5]. Moreover, dynamic computing with chaotic logic devices has been suggested [6].

In this paper, we propose a logic device that includes a chaotic transition state and uses the chaotic neuron model.

Logic functions of the proposed circuit can be dynamically changed. We furthermore experimentally construct the proposed device using switched-capacitor chaotic neuron circuits, and confirm the fundamental properties of the proposed circuit through experimentation.

#### 2. Chaotic Neuron Model

The chaotic neuron model [3] is described by

$$y(t+1) = ky(t) + \sum_{j=1}^{N} v_j A_j(t) - \alpha x(t) - \theta(1-k), (1)$$

$$x(t+1) = f(y(t+1)), \qquad (2)$$

where y(t), x(t), and  $A_j(t)$  are the internal state, the output, and the jth input of the chaotic neuron, respectively, at a discrete time t.  $k(0 \le k < 1)$  is the damping factor of the internal state,  $\alpha(\alpha \ge 0)$  is a parameter for the refractoriness,  $\theta$  is a threshold, and  $v_j$  is a connection strength from the external input  $A_j(t)$ . f(y) is a continuous output function given by

$$f(y) = \frac{2}{1 + \exp(-y/\epsilon)} - 1,$$

(3)

where  $\epsilon$  is a gain parameter.

## 3. Logic Circuit with Chaotic Neuron Model

#### 3.1. Construction of a logical device

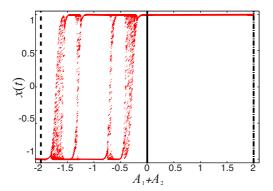

We relate the input–output characteristic of the chaotic neuron and logic states as follows. As an example, Fig. 1 shows the input–output characteristic of a chaotic neuron that has two inputs  $A_1$  and  $A_2$  with k=0.5,  $\alpha=0.8$ ,  $\epsilon=0.03$ ,  $v_1=v_2=1$ , and  $\theta=-2$ .

We set the value 1 to logical "true," and -1 to logical "false." In Fig. 1, when  $A_1 \simeq A_2 \simeq -1$ , the output is -1, therefore corresponding to false near the dotted line. When  $A_1 \simeq 1$  and  $A_2 \simeq -1$ , or vice versa, the value  $A_1 + A_2$  is near the solid line in Fig. 1, and the output value is 1 (true). For  $A_1 \simeq A_2 \simeq 1$  (near the chain line), the output is 1 (true). As a consequence, with  $A_1, A_2 \in \{-1, 1\}$ , the chaotic neuron in this example operates as a logical OR function. Table 1 summarizes the truth table of the above operation.

<sup>\*</sup>Currently with the Graduate School of Information Science and Technology, Hokkaido University.

Fig. 1: Input–output characteristic of a chaotic neuron model with two inputs  $A_1$  and  $A_2$  (k = 0.5,  $\alpha = 0.8$ ,  $\epsilon = 0.03$ ,  $v_1 = v_2 = 1$ ,  $\theta = -2$ ).

Table 1: Truth table for the characteristic of the chaotic neuron with two inputs shown in Fig. 1.

| $A_1$ | $A_2$ | x(t) |

|-------|-------|------|

| -1    | -1    | -1   |

| -1    | 1     | 1    |

| 1     | -1    | 1    |

| 1     | 1     | 1    |

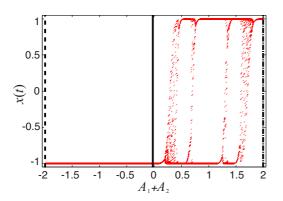

Figure 2 shows another example with  $\theta=2$ . Here, when  $A_1\simeq A_2\simeq 1$  the output is false, that is, the output value is -1 near the dotted line. Moreover, near the solid line the output is -1,(false) for  $A_1\simeq 1$  and  $A_2\simeq -1$ , and vice versa. The output is 1 (true) near the dash-dotted line in Fig. 2 where  $A_1\simeq A_2\simeq 1$ . In this case, therefore, the chaotic neuron operates as a logical AND function.

As shown in the above examples, resulting logic functions can be changed according to the value of  $\theta$ . In addition, if we set  $v_1 = v_2 = -1$  in Fig. 1 and Fig. 2, NAND and NOR functions are realized, respectively.

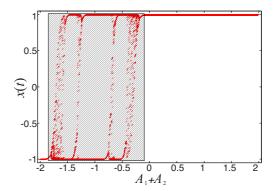

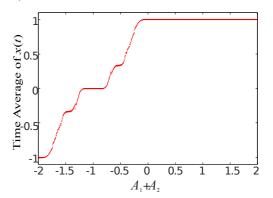

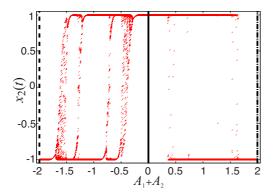

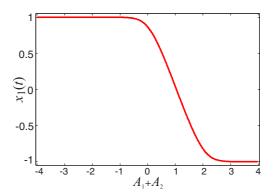

Figure 3 highlights the response for the input range  $-2 < A_1 + A_2 < 0$ . As shown in the shaded area, the response includes periodic and chaotic states. Figure 4 shows the longtime average of x(t) in Fig. 3. We can exploit the transition characteristic of the chaotic neuron as a novel

Fig. 2: Input–output characteristic of the chaotic neuron  $(\theta = 2.k = 0.5, \alpha = 0.8, \epsilon = 0.03, v_1 = v_2 = 1)$ .

Fig. 3: Response for the intermediate input values of the chaotic neuron (k = 0.5,  $\alpha = 0.8$ ,  $\epsilon = 0.03$ ,  $v_1 = v_2 = 1$ ,  $\theta = -2$ ).

Fig. 4: Long-time average of x(t) in Fig. 3.

computational device. Moreover, the characteristic can be dynamically controlled, as demonstrated above.

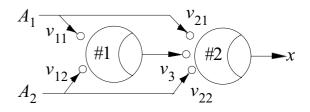

Next, we construct an EXOR logic circuit with two cascaded chaotic neurons. For intermediate input values, the EXOR circuit also shows chaotic and periodic responses. We start from an EXOR circuit consisting of two chaotic neurons, as shown in Fig. 5. In Fig. 5, we set  $v_{11} = v_{12} = -1$  and  $\theta_1 = -2$  in the first neuron, and  $v_{21} = v_{22} = 1$ ,  $v_3 = 2$ , and  $\theta_2 = 2$  in the second neuron. We set k = 0.5,  $\epsilon = 0.03$ , and  $\alpha = 0.7$  for both chaotic neurons.

Figure 6 shows the input-output characteristic of Fig. 5.

Fig. 5: Schematic diagram of the EXOR circuit with two chaotic neurons.

Fig. 6: EXOR characteristic from the two-stage chaotic neuron circuit in Fig. 5.

Here, when  $A_1 \simeq A_2 \simeq -1$  (near the dotted line), the output value is -1 (false). The output value is 1 (true) near the solid line, that is,  $A_1 \simeq 1$  and  $A_2 \simeq -1$ , and vice versa. Moreover, the output value is -1 (false), near the dash-dotted line with  $A_1 \simeq A_2 \simeq 1$ . Therefore, as shown in Table 2, the circuit in Fig. 5 operates as a logical EXOR function.

The intermediate characteristics in the transition regions are not symmetric, however, as shown in Fig. 6. We therefore change the parameters to realize a symmetrical response. First, we increase  $\epsilon_1$  in the first neuron to 0.5 to decrease the steepness of the response for the input values between 0 and 1. Second, we set  $v_{11} = v_{12} = -1$ ,  $\theta_1 = -2.6$ , k = 0.6,  $\alpha_1 = 0.6$ ,  $v_{21} = v_{22} = 1$ ,  $\theta_2 = 2.6$ ,  $\alpha_2 = 0.5$ ,  $\epsilon_2 = 0.03$ , and  $v_3 = 2$ .

Figure 7 shows the input–output characteristic of the circuit in Fig. 5 after the above changes; the circuit performs the EXOR function for logical true and false inputs, and the response is symmetric with respect to  $A_1 + A_2 = 0$ .

Table 2: Truth table of the EXOR characteristic in Fig. 6.

|                | -1 1<br>1 1 | 1                |           |

|----------------|-------------|------------------|-----------|

|                | 1 -1        | 1                |           |

|                | 1 1         | -1               |           |

| 4 (* -         |             |                  | <u> 1</u> |

| '[: <i>[</i> [ |             | W V              | <b>\</b>  |

|                |             |                  |           |

| 0.5            |             |                  |           |

|                | A I         | W 1              | 1         |

| $\Xi$          |             |                  |           |

| $\chi_2(t)$    |             |                  |           |

|                |             |                  | Ž.        |

| -0.5           | 1 8         |                  |           |

|                | . E         |                  |           |

| ئلىشارىي       |             | السالما المسالما |           |

| -2 -1.5        | -1 -0.5 0   | $A_2$ 0.5 1      | 1.5 2     |

|                | $A_1$ +     | $A_2$            |           |

Fig. 7: EXOR characteristic after adjusting parameters.

Fig. 8: Input–output characteristic of the first stage of the chaotic neuron after  $\epsilon_1$  is increased to 0.5.

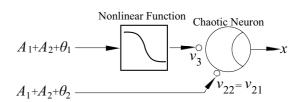

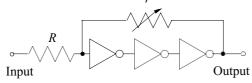

Figure 8 shows the input—output characteristic of the first chaotic neuron with  $\epsilon_1 = 0.5$ . As shown in the figure, the first chaotic neuron does not indicate chaos; rather, the response is smooth like a sigmoidal function. We can therefore efficiently construct an EXOR by replacing the first neuron in Fig. 5 with a simple nonlinear function circuit, as shown in Fig. 9.

# 4. Circuit Implementation and Experiments with Discrete Elements

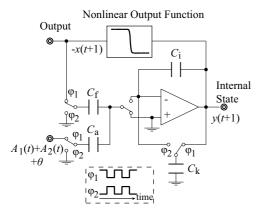

We constructed the EXOR logic circuit shown in Fig. 9 using a switched-capacitor (SC) circuit technique [7]. Figure 10 shows the SC chaotic neuron circuit. The supply voltages are  $\pm 8$  V. Equations (4) and (5) determine the parameters k and  $\alpha$ , respectively:

$$k = 1 - \frac{C_k}{C_i},\tag{4}$$

$$\alpha = \frac{C_f}{C_i}. (5)$$

$v_1 = v_2 = 1$  is realized by setting  $C_a/C_i = 1$ . The threshold  $\theta$  is added to the input as shown in Fig. 9 in the experiments. We realized the nonlinear function in Fig. 9 with the CMOS inverter circuit shown in Fig. 11.

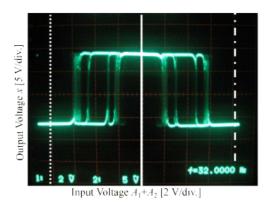

Figure 12 shows the input–output characteristic of the circuit of Fig. 9 for  $\alpha = 0.1$ , k = 0.76,  $\theta_1 = -5.5$  V,  $\theta_2 = 3$  V,  $v_{21} = v_{22} = 0.45$ , and  $v_3 = 0.3$ . In the figure, a +4 V input voltage corresponds to logical true, and -4

Fig. 9: Schematic diagram of the EXOR circuit with a nonlinear function circuit and a chaotic neuron.

Fig. 10: SC chaotic neuron circuit.

Fig. 11: CMOS inverter circuit; the resistor r is used to adjust gain.

V corresponds to false. Moreover, +8 V and -8 V output voltages correspond to true and false, respectively.

As shown in Fig. 12, when  $A_1 \simeq A_2 \simeq -4$  V, the output voltage around the dotted line is false (-8 V). Similarly, around the dash-dotted line the output voltage is -8 V (false). When  $A_1 \simeq 4$  V and  $A_2 \simeq -4$  V, and vice versa, the output is 8 V (true). Therefore, the circuit shown in Fig. 9 operates as a logical EXOR function, as summarized in Table 3.

Fig. 12: Measured input–output characteristic of the EXOR circuit in Fig. 9 ( $\alpha = 0.1$ , k = 0.76,  $\theta_1 = -5.5$  V,  $\theta_2 = 3$  V,  $v_{21} = v_{22} = 0.45$ , and  $v_3 = 0.3$ ).

Table 3: Truth table of the characteristic in Fig. 12.

| $A_1$ [V] | $A_2$ [V] | <i>x</i> ( <i>t</i> ) [V] |

|-----------|-----------|---------------------------|

| -4        | -4        | -8                        |

| -4        | 4         | 8                         |

| 4         | -4        | 8                         |

| 4         | 4         | -8                        |

#### 5. Conclusion

We proposed dynamic logic circuits using chaotic transition regions with chaotic neurons. The proposed circuits operate as logic functions with input values near logic values. At intermediate input values the proposed circuits show chaotic and periodic responses. Functioning of the circuit can be dynamically altered. In the EXOR circuit implementation, we simplified the circuit by employing a simple inverter as the first stage of the two-chaotic neuron structure. We have shown experimental results from the SC circuit implementation for the EXOR circuit.

In future research, we will examine dynamic logic systems using the proposed device. We will furthermore use the chaotic transition regions to construct a novel computational system.

### Acknowledgments

This research is partially supported by the Aihara Innovative Mathematical Modelling Project, the Japan Society for the Promotion of Science (JSPS) through the "Funding Program for World-Leading Innovative R&D on Science and Technology (FIRST Program)," initiated by the Council for Science and Technology Policy (CSTP), and Kakenhi (20300085).

#### References

- [1] W. S. McCulloch and W. H. Pitts, "A logical calculus of the ideas immanent in neural nets," Bull. Math. Biophys., vol. 5, pp. 115–133 1943.

- [2] A. L. Hodgkin and A. F. Huxley, "A quantitative description of membrane current and its application to conduction and excitation in nerve," J. Physiol., vol. 117, pp. 500–544, 1952.

- [3] K. Aihara, T. Takabe and M. Toyoda, "Chaotic neural networks," Phys. Lett. A, vol. 144, pp. 333–340, 1990.

- [4] Y. Horio and K. Aihara, "Analog conputation through high-dimensional physical chaotic neuro-dynamics," Physica-D, vol. 237, no. 9, pp. 1215–1225, 2005.

- [5] Y. Horio, H. Ando and K. Aihara, "Fundamental technology for complex computational systems," IEICE Fundamentals Review, vol. 3, no. 2, pp. 34–44, 2009.

- [6] T. Munakata, J. Takahashi, M. Sekikawa and K. Aihara, "Chaos computing: A unified view," International Journal of Parallel, Emergent and Distributed Systems, vol. 25, no. 1, pp. 3–16, 2010.

- [7] Y. Horio and K. Suyama, "Switched-capacitor chaotic neuron for chaotic neural networks," in Proc. IEEE Int. Symp. Circuits Syst., pp. 1018–1021, Chicago, IL, May, 1993.