## A Neuromorphic Single-Electron Circuit for Noise-Shaping **Pulse-Density Modulation**

Andrew Kilinga Kikombo, Hokkaido University, Japan Tetsuya Asai, Hokkaido University, Japan Takahide Oya, Yokohama National University, Japan Alexandre Schmid, Swiss Federal Institute of Technology (EPFL), Switzerland Yusuf Leblebici, Swiss Federal Institute of Technology (EPFL), Switzerland Yoshihito Amemiya, Hokkaido University, Japan

### **ABSTRACT**

We propose a bio-inspired circuit performing pulse-density modulation with single-electron devices. The proposed circuit consists of three single-electron neuronal units, receiving the same input and are connected to a common output. The output is inhibitorily fedback to the three neuronal circuits through a capacitive coupling. The circuit performance was evaluated through Monte-Carlo based computer simulations. We demonstrated that the proposed circuit possesses noise-shaping characteristics, where signal and noises are separated into low and high frequency bands respectively. This significantly improved the signal-tonoise ratio (SNR) by 4.34 dB in the coupled network, as compared to the uncoupled one. The noise-shaping properties are as a result of i) the inhibitory feedback between the output and the neuronal circuits, and ii) static noises (originating from device fabrication mismatches) and dynamic noises (as a result of thermally induced random tunneling events) introduced into the network. [Article copies are available for purchase from InfoSci-on-Demand.com]

Single-electron, pulse-density modulation, noise-shaping, fault-tolerant, defect-tolerant, neuro-Keywords: morphic LSIs, reliable circuit design, Beyond CMOS architectures

### INTRODUCTION

For the past 3 decades, the scaling of semiconductor devices has been the primary driving force behind improving the performance of LSI processors and systems. The decreasing feature sizes of transistors have been accompanied by dramatic increase in speed and integration densities, which have in turn led to increased and diversified functionality. This trend has been viable mainly due to guaranteed reliability in the downscaled devices even with decreasing process technologies. Reliability corresponds to high yields per die, hence low production costs (high cost efficiency), giving the circuit designer the opportunity to create reliable integrated systems with improved processing speeds, and increased functionality.

However, as the physical feature sizes approach the deep sub-micron regime, process variations and undesirable internal (and or external) noises associated with nano-scale properties pose critical concerns in the future of scaling and in system system design; they dramatically reduce the reliability of electronic devices on the edge of the nano-scales (Bowman, 2002; Constantinescu, 2003; Jose, 2003; Way & Taeho, 1999). This reduced reliability is even more conspicuous as electronic device sizes are further scaled down to the nano-meter regime (Calhoun, 2008; Orshansky, 2002; Stolk, 1998).

Getting rid of these nano-scale characteristics would involve introducing error-detecting circuits within the system, which leads to advanced complexity, and design tradeoffs in using high integration capacities available to the circuit designer. Some design techniques offering possible ways to mitigate the impact of within-die variations have been explored (Marculescu & Talpes, 2005; Tiwari, 2007). Other works involving introducing error-detecting circuitry in electronic systems include architectures proposed by Milor (1989) and Chatterjee (1993). Unfortunately, these approaches offer only a short term solution. The uncertainty in coming up with a long-lasting solution to these challenges has paved the way into a new field of the so called *emerging research nano devices*, which effectively utilize nano-scale characteristics in their operation. Such devices are viewed as promising blocks for creating application-specific processors, and ultra low-power systems in coming generations of LSI platforms. Such devices would include single-electron devices (Grabert & Devoret, 1992; Nakajima, 1997).

Single-electron devices inherently operate with extreme low power dissipation, and provide a high integration density per unit area. Thus, they are viewed as potential building blocks for low-power, parallel-based computational applications in future LSI platforms. However, one of the major problems facing single-electron devices is that they are potentially *unreliable*. Their low reliability originates from two factors: i) large variations in the features of fabricated devices, hence device characteristics, and ii) sensitivity to internal and external noises. Therefore, despite all the appealing features in utilizing nano-electronic devices in future electronic systems, we have to address and solve a fundamental question; how do we build reliable systems from error-prone building devices?

Improvements in fabrication technology alone cannot accomodate such enormous device failures. Therefore in designing functional electronic devices in the deep sub-micron and postsilicon era, we need to keep in mind the fact that we have to build reliable systems with unreliable (ITRS, 2005), and error-prone devices (Nikolic, 2001; Schimid & Leblebici, 2004; Goser, 1997). Thus the need to address robustness and design systems with large enough signal-to-noise ratio is inevitable (Hamed, 1997).

An innovative architectural approach to increasing reliability is to exploit the internal and external noises, and the heterogeneity originating from fabrication mismatches in designing new electronic systems. For example, if we look at how living organisms code and transmit signals in their systems, we find similarities between neurons (the basic elements responsible for information processing in neuronal systems) and nano-meter sized electronic devices. Neurons are sensitive to noises, operate asynchronously because of differences in their structural properties, and have large time jitters—that is, they are imperfect and unreliable (Shadelen & Newsome, 1998; Shint, 1993; Softky, 1993)—-but nevertheless they carry out information processing effectively. Similarly, nano-electronic devices (for instance single-electron devices) are sensitive to external interferences and noises, and have diverse fabrication variations in feature sizes, resulting in heterogeneity in parameters and device characteristics. Thus in creating electronic systems with such imperfect units, obtaining hints from living organisms is evidently of much importance. Such electronic systems that mimic neurological systems are referred to as neuromorphic circuits (Douglas, 1995; Mead, 1998). A number of neuromorphic circuits that operate by utilizing noises and device fabrication mismatches have been proposed. They include neuromorphic CMOS circuits utilizing device fabrication mismatches and environmental noises (Utagawa, 2007), singleelectron circuits employing thermally induced stochastic resonance (SR) (see Collins (2002) for details on SR) in signal transmission (Oya, 2007), and single-electron networks performing synchrony detection (Oya, 2006).

This paper explores the possibility of creating novel circuit architectures with single-electron devices, by employing environmental (dynamic) noises, and static noises originating from fabrication mismatches. The circuit architecture is inspired by information coding mechanisms in biological neural networks that convert analog input signals into spike densities (digital-pulse streams) in the time domain. This operation is also referred to 1-bit analog-to-digital conversion, and is often implemented with  $\Delta\Sigma$  modulators (Aziz, 1996; Schreier & Temes, 2004). Such converters exhibit noise-shaping properties (see Mayr & Schueffny (2005); Shin (2001-a); Shin (2001-b)) for details on neuronal noise-shaping), separating signal and noises into low and high frequency bands respectively. A theoretical investigation of noise-shaping in neural networks is elaborated by Mar (1999). In their work, they demonstrated that noise-shaping was improved by introducing an inhibitory coupling between noisy model integrate-and-fire neurons (IFNs). In addition, the authors note that the noise-shaping properties were improved due to heterogeneity and noises introduced into the network. Inspired by their work, we propose and investigate the performance of a single-electron pulse-density modulating circuit that exhibits noise-shaping properties.

This paper is organised as follows. Firstly, a brief review of pulse-density modulation in neurons is presented. Secondly, implementation of integrate-and-fire neurons, together with fundamental operation of single-electron devices is illustrated. Thirdly, a model on how to realize pulse-density modulation employing excitatory and inhibitory mechanisms is explained. This is followed by the circuit structure implementing the model with single-electron oscillators. Fourthly, the performance of the proposed circuit is investigated. The paper is summarized by noting on a possible architecture that also employs noises in achieving improved signal-to-noise ratio in single-electron circuits and nanowire transistor networks.

### A SHORT REVIEW OF PULSE-DENSITY MODULATION IN NEURONS

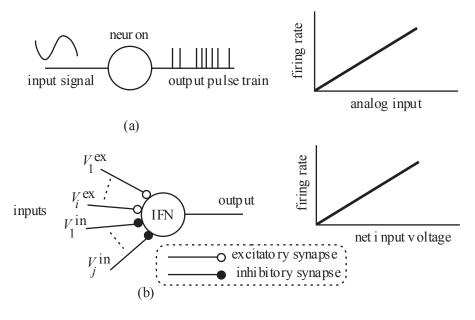

A neuron aggregates inputs from other neurons connected through synapses. The aggregated charge raises the membrane potential until it reaches a threshold, where the neuron fires generating a spike. This spike corresponds to a binary output 1 . After the firing event, the membrane potential is reset to a low value, and it increases again as the neuron accepts inputs from neighboring neurons (or input signals) to repeat the same cycle; producing a stream of one and zero pulse trains. The spike interval (density of spikes per unit time) is proportional to the the analog input voltage i.e. the level of analog input is coded into pulse density. Thus a neuron can be considered as a 1-bit A-D converter (Cheung & Taung, 1993; Hovin, 2002) operating in the temporal domain. Figure 1(a) shows a schematic representation of analog-todigital conversion in neurons. The output pulse density is proportional to the amplitude of the input signal. The operation of neurons is often modeled with spiking neurons such as the integrate-and-fire neurons. Figure 1(b) illustrates the fundamental operation of an integrate-and-fire (IFN) neuron. The open circles (•) and shaded circles (•) represent excitatory and inhibitory synapses, respectively. The IFN receives input signals (voltages) through the excitatory synapses (to raise its membrane voltage) and inhibitory synapses (which decrease the membrane voltage) from adjacent neurons, to produce a spike if the summed input voltage ( $\sum$  $V_i^{\text{ex}} - \sum V_i^{\text{in}}$ ) exceeds the threshold voltage. After the IFN fires, its membrane voltage is reset to a low value, and the integration action resumes.

The output pulse density is proportional to the net input voltage.

# SINGLE-ELECTRON INTEGRATE AND FIRE NEURON

A single-electron oscillator (Averin & Likharev,1986; Grabert & Devoret, 1992; kikombo, 2008, Likharev & Zorin, 1985; Oya, 2005) is used to model the operation of an integrate-and-fire neuron (IFN). A single-electron oscillator (Figure 2(a)) consists of a tunneling junction (capacitance =  $C_j$ ) and a high resistance R connected in series at the node (•) and biased with a positive or a negative voltage  $V_d$ . It produces self-induced relaxation oscillations if the bias voltage is higher than the tunneling threshold  $(V_d > e/(2C_j))$  (where e is the elementary charge and  $k_B$  is the Boltzmann constant). The node volt-

age  $V_1$  increases as the capacitance  $C_1$  is charged through the series resistance (curve AB), until it reaches the tunneling threshold e/(2C), at which an electron tunnels from the ground to the nanodot across the tunneling junction, resetting the node voltage to -e/(2C). This abrupt change in node potential (from B to C) can be referred to as a firing event. The nanodot is recharged to repeat the same cycles. Therefore, a single-electron oscillator could be viewed as an integrate-and-fire neuron, which aggregates input voltages (or inputs from neighboring neurons) producing a pulse when its node voltage reaches the threshold voltage (Figure 2(b)). By feeding a sinusoidal input to a singleelectron oscillator, one can adjust the probability of electron tunneling in the circuit: the tunneling rate increases as the input voltage rises above the threshold and gradually decreases to zero as the input approaches and falls below the threshold value. In other words, a single-electron oscillator converts an analog input into digital pulses. A single-electron oscillator can thus be viewed

Figure 1. (a) Pulse density modulation in neurons: analog input is converted into a pulse train whose density is proportional to the net amplitude of the input signal. (b) Fundamental structure and operation of integrate-and-fire neurons (IFNs). The IFN receives input voltages through excitatory and inhibitory synapses, and produces pulses when the net input voltage exceeds the threshold. The output pulse density (firing rate) is proportional to the net input voltage.

as a PDM converter, that produces a spike train (or produces zero) if the input signal exceeds (or falls below) the threshold value.

### CIRCUIT IMPLEMENTATION

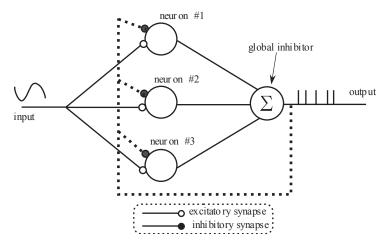

Figure 3 shows the model of the proposed circuit, consisting of three neuronal elements. The neurons receive the same analog input through excitatory synapses ( $\circ$ ) and produce digital pulses toward the global inhibitor  $\Sigma$  (Asai; 2003). The output is fed-back to the three elements through inhibitory synapses denoted by shaded circles ( $\bullet$ ) in the network. Firing in any of the neurons in the network decreases the membrane potential of the other neurons, reducing the probability of their firing.

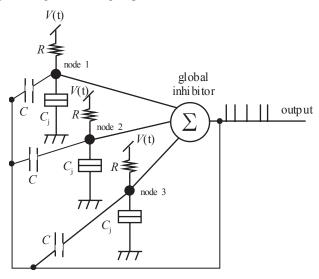

The neuronal structure in Figure 3 is implemented with single-electron oscillators that receive the same analog input. The input induces electron tunneling in the single-electron oscillators, generating pulses toward the global inhibitor. The global inhibitor  $\Sigma$  sums the pulses to produce a train of spikes representing

tunneling (firing) events in the three neurons. Figure 4 shows the circuit configuration. Each neuron in the network is implemented with a single electron oscillator. The global inhibitor is realized by numerically summing the firing events in the network. Inhibitory synapses are implemented by coupling capacitances (*C*) that decrease the node voltages of all the oscillators once a pulse is released at the output.

Each neuron in the network receives the same input (V(t)) raising its node voltage. Whenever any of the three single-electron oscillators reaches its threshold voltage, it fires, releasing a pulse toward the global inhibitor. The global inhibitor, through the coupling capacitors C, subtracts a certain amount of voltage from the other oscillators, suppressing them from tunneling for a certain period of time. This contributes to the distribution of output pulses. In the absence of the global inhibitor, all the neurons would fire randomly and with almost the same timing, producing a Poissonlike distribution of inter-spike intervals (ISIs). Contrally, by introducing the global inhibitor, consecutive firing events in the network are sup-

Figure 2. Single-electron tunneling (SET) oscillator: (a) circuit configuration and (b) waveform showing oscillation of node voltage  $V_p$ , as capacitor  $C_j$  is charged through resistance R (from A to B) and reset by an electron tunneling from the ground to the node (voltage drop from B to C). This sudden drop in the node voltage (BC) corresponds to a pulse output.

Figure 3. Model of pulse-density modulation circuit employing excitatory and inhibitory mechanisms. A common input is fed to the three neurons through excitatory synapses (•), while the output is fedback to the three neurons through inhibitory synapses (•).

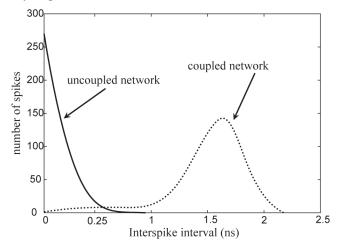

pressed, resulting in a Gaussian-like distribution of ISIs in the coupled network.

### SIMULATION RESULTS

As mentioned in the introduction, the noiseshaping properties of the network of model neurons were reportedly improved by introducing dynamic and static noises (Mar, 1999). In our circuit, this was realised as follows. As noted earlier, thermal noises lead to random electron tunneling in single-electron devices. We therefore introduced dynamical noises by tuning the temperatures in both the coupled and the uncoupled networks. Static noises were introduced only in the coupled network, by varying the values of series resistances R. In the coupled network, all the series resistances were set to 44 M $\Omega$ , whereas in the coupled network, the mean value of the three resistances was 44 M $\Omega$ , and the variance was  $\pm 12.5\%$ . The inhibitory coupling in the coupled network was implemented with a capacitive coupling of 4 aF. The temperature was set to 0.5 K in all simulations.

The performance of both the coupled and the uncoupled circuits was investigated through Monte-Carlo based computer simulations. All the circuit units in both the coupled and the uncoupled networks were fed with a sinusoidal input  $V(t) = V_0 + A\sin(2\pi ft)$ , where amplitude A = 2.5 mV, frequency f = 100 MHz, and bias voltage  $V_0 = 7.85$  mV.

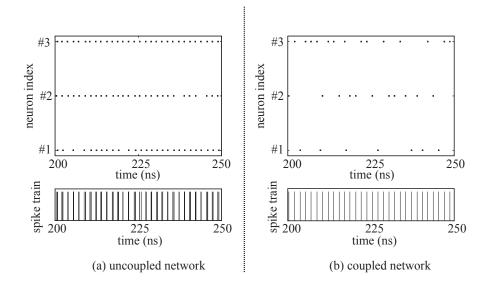

Figure 5 shows the raster plots of the firings of the network elements. The top diagrams of (a) and (b) show the random pulses for each unit in the uncoupled and coupled networks, respectively. The bottom diagrams in (a) and (b) show the summed output (pulse train) for all the elements in the uncoupled and coupled networks, respectively. From the diagrams, we could observe that the firing timings in the uncoupled network were random and all the neurons fired with almost the same timing. In the coupled network, however, the firing of one of the neurons inhibited the others from firing, thus reducing the probability of consecutive firing in the network. In addition, the variance in the series resistances results in variations in the time constants of the network neurons. This reduced the probability of neurons attaining the firing threshold at the same time, and thus

Figure 4. Single-electron circuit performing pulse-density modulation. The structure consists of three single-electron oscillators, and a global inhibitor  $\Sigma$ . The output is fed back to all the other oscillators through the capacitive coupling C.

improved the distribution of firing intervals in the network. Consequently, these two factors resulted in well distributed firing timings in the network, leading to a Gaussian-like distribution of inter-spike intervals.

Figure 6 shows the ISI distribution of firing events in the whole network. The histogram for the coupled network shows a Gaussian-like distribution with an inter-spike interval of 1.65 ns at the maximum number of firing counts. The histogram for the uncoupled network, in contrast, shows a Poisson-like distribution. We also investigated the effect of increasing the variance in the series resistances on the standard deviation of the Gaussian-like distribution. We found that the standard deviation increases as the variation decreases below or increases above 12.5 %. As the variance decreases, the probability that multiple neurons in the network reach the threshold voltage at the same time increases. This shifts the ISI at the maximum firing rate toward zero, consequently leading to a larger standard deviation of the ISI distribution. The ISI distribution can, however, be tuned by adjusting the value of the inhibitory coupling capacitance C. As the coupling strength increases, the number of neurons reaching the threshold concurrently decreases drastically. In other words, the firing timings tend to distribute evenly, resulting to a sharper Gaussian-like distribution. However, increasing the coupling strength to a relatively high value, beyond an optimal value (of 4 aF in our simulations), leads to a winner-takes-all (Cohen & Grossberg, 1983; Kaski & Kohen, 1994) operation (where only one neuron in the network produces the highest spike rate and inhibits all the others from firing). This would be undesirable, especially in a network of fault- and defect-prone elements, where increasing the probability of correct operation requires that all the elements play a substantial part in the network operation (i.e. a winners-share-all (Fukai & Tanaka, 1997) operation, where several neurons in the network survive). Thus obtaining an ideal operation of the network requires tuning the firing rates of individual neurons though the series resistances, and also tuning the summed firing rate of the network through the capacitive coupling to obtain a winners-share-all type function.

Figure 5. Raster plots for firing events for uncoupled (left diagrams) and coupled (right diagrams) networks. The top diagrams show firing events for each neuron, while the bottom diagrams show summed output spike train at the global inhibitor  $\Sigma$ . Firing events in the uncoupled network were random and almost consecutive, whereas firing timings in the coupled network were well distributed as a result of the inhibitory coupling inhibiting concurrent events.

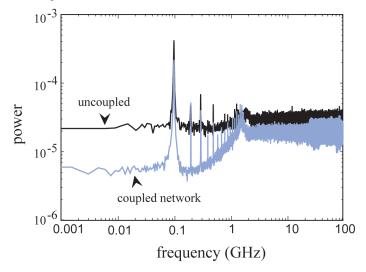

Figure 7 shows the power spectra for the coupled and uncoupled networks. The power in both cases was calculated with 25 runs averaged with a square window. From the results we can confirm that the global inhibitory coupling and the heterogeneity in series resistances collectively helped reduce the noise level in the coupled network substantially. The signalto-noise ratio in the uncoupled network was 22.96 dB, while that in the coupled network was 27.30 dB below the cutoff frequency of 1 GHz. The harmonic distortions in the results are due to (i) the intrinsic firing rates of the individual neurons in the network and (ii) nonlinear feedback introduced to the network. These distortions degraded the SNR characteristics. They could be decreased by setting the input signal frequency to a value much lower than the firing frequencies of individual neurons in the network. Another way of increasing the SNR without tuning the input frequency would be by filtering the output signals, to get rid of the higher frequencies. This is often realized with digital filters in the feedback loop of  $\Sigma\Delta$  converters (Kim, 2007).

## DISCUSSIONS AND CONCLUSION

To provide a basis for designing electronic circuits with mismatch-prone single-electron devices, this paper proposed and investigated the performance of a bio-inspired 1-bit analog-to-digital converter. The circuit elements are coupled to each other through a global inhibitory coupling. Through Monte-Carlo based computer simulations, we demonstrated that the presence of static and dynamic noises, and the global inhibitory coupling introduced into the circuit play an important role in improving its noise-shaping properties. The signal-to-noise ratio improved by 4.34 dB in the coupled network as compared to the un-coupled one.

Figure 6. Histogram of inter-spike intervals (ISIs) for coupled and uncoupled networks. The uncoupled network shows a Poisson-like distribution of ISIs where the firing events in the network elements are almost concurrent. The coupled network shows a Gaussian-like distribution, as a result of distributed firing events.

Figure 7. Power spectra of coupled and uncoupled networks. The coupled network shows a reduced noise level in the lower frequencies (signal band), improving the SNR with 4.34 dB as compared to the uncoupled network.

In the present network we extensively investigated the effect of static noises as a result of variations in series resistances, and of the inhibitory coupling in the network to noiseshaping properties. Investigating the effect of dynamic noises at higher temperatures, would

also give a guideline into actual circuit design with such noise sensitive devices. From the results of these investigations, we can deduce that the performance of the circuit would improve up to the optimal value of thermal noises, and then deteriorate drastically as randomly induced firing further increases. This is as a result of decreased effect of the inhibition strength which contributes to the Gaussian-like distribution as discussed in the simulation results.

Also, choosing the optimal number of neurons to use in the network would play an important role in improving its performance. As the number of neurons increases, we would obtain better resiliency toward faults and defects in the network. This would however, come at the expense of tuning the optimal inhibitory coupling strength to realize a winners-share-all operation.

Before summarizing the paper, it's worth noting on similar promising works in achieving robust electronic systems by utilizing noises in improving signal-to-noise ratio in electronic systems. This approach has been demonstrated with single-electron devices (Oya, 2007), and nanowire transistor networks (Kasai & Asai, 2008) by some of the authors of this paper. The architectures effectively employ stochastic resonance (SR) (Collins, 2002), and demonstrate a viable novel approach to realizing robust systems in noisy environments. Stochastic resonance is a phenomenon where weak signals can be retrieved from a noisy output (Gammaitoni, 1998; Simonotto, 1997) by applying an optimal amount of random noise. Oya (2007) proposed a single-electron neural network that utilizes SR in signal transmission in neural networks, and successfuly demonstrated that using SR indeed improved the temperature performance of the circuit. Kasai and Asai (2008) experimentally investigated the performance of nanowire transistors with variations in threshold voltages and operating in a noisy experimental setup. In both cases, the effects of SR were investigated by setting the input signal to a value lower than the tunneling (firing) threshold of the network elements. By applying noises, network elements with non-zero inputs were induced to tunnel—tunneling events synchronized with the input signal to a certain quantity of noises. The authors showed that the SNR in their circuits was enhanced through partially using noises.

Such innovative approaches, in addition to the *neuromorphic* methodology described in

this paper would be indispensable in addressing reliability issues in electronic circuitry with nano-electronic devices. From the investigation results in this paper, we can conclude that by learning from biological systems: high levels of redundancy where information processing depends on many neurons operating in parallel, controlled signal transfer through excitatory and inhibitory synapses, and stochastic resonance mechanisms, we could get hints on how to design circuits that perform better even in noisy environments and (or) with failure-prone electronic devices.

### **REFERENCES**

Asai, T., Kanazawa, Y., & Amemiya, Y. (2003). A subthreshold MOS neuron circuit based on the volterra System. *IEEE transactions on neural networks*, 14, 5, 13081312.

Averin, D.V., & Likharev, K.K. (1986). Coulomb blockade of single-electron tun neling, and coherent oscillations in small tunnel junctions. *J. of Low Temp. Phys.*, 62,345-373.

Aziz, P.M., Sorensen, H.V., Van der Spiegel, J. (1996). An overview of sigma-delta converters. *IEEE Signal Processing Magazine*, 13, 61-84.

Bowman, K., Duvall, S., & Meindl, J. (2002). Impact of die-to-die and within die parameter fluctuations on the maximum clock frequency distribution for gigascale integration. *J. of Solid-State Circuits*, 37, 183-190.

Calhoun, B.H., Cao, Y., Xi L., Mai, K., Pileggi, L.T., Rutenbar, R.A., & Shepard, K.L. (2008). Digital Circuit Design Challenges and Opportunities in the Era of Nanoscale CMOS. *Proc. of the IEEE*. 96, 343-365.

Chatterjee, A. (1993). Concurrent Error Detection and Fault-Tolerance in Linear Analog Circuits Using Continuous Checksums. *IEEE Transactions on very large scale Integration (VLSI) Systems*, 1, 138–150.

Cheung, K.F., & Taung, Y.H.P. (1993). Sigma-Delta modulation neural networks. *Proc. 1993 IEEE Int. Symposium on Circuits and Systems*, 489-493.

- Collins, J.J., Chow, C.C., & Imhoff, T.T. (2002). Stochastic resonance without tuning. *Nature*, 376, 236-238.

- Cohen, M.A., & Grossberg, S. (1983). Absolute stability of global pattern formation and parallel memory storage bycompetitive neural networks. IEEE Transactions on Systems, Man and Cybernetics, 13, 815-826.

- Constantinescu, C. (2003). Trends and challenges in VLSI circuit reliability. *Micro*, *IEEE*, 23, 14 - 19.

- Douglas, R., Mahowald, M., & Mead, C. (1995). Neuromorphic Analogue VLSI. Annual Review of Neuroscience, 18, 255-281.

- Fukai, T., & Tanaka, S. (1997). A simple neural network exhibiting selective activation of neuronal ensembles: from winner-take-all to winners-share-all. Neural Computation 9, 77-97.

- Gammaitoni, L., Hanggi, P., Jung, P., & Marchesoni, F. (1998). Stochastic resonance. Reviews of Modern Physics, 70, 1.

- Goser, K.F., Pacha, C., Kanstein, A., & Rossmann, M.L. (1997). Aspects of systems and circuits for nanoelectronics. Proc. of the IEEE, 85, 558-573.

- Grabert, H., & Devoret, M.H. (1992). Single Charge Tunneling—Coulomb Blockade Phenomena in Nanostructures. New York: Plenum.

- Hamed, H. (1997). Single electron devices: challenge for nanofabrication. J. of vac. Sci & Tech., 15, 2101.

- Hovin, M., Wisland, D., Berg, Y., Marienborg, J.T., & Lande, T.S. (2002). Delta Sigma modulation in single neurons. Proc. 2002 IEEE International Symposium on Circuits and Systems, 5, 617-620.

- International technology roadmap for semiconductors, ITRS, (2005).

- Jose A. B. F. (2003). Future Challenges in VLSI Design. IEEE Computer Society Annual Symposium on VLSI (ISVLSI'03), 5-7.

- Kasai, S., & Asai, T. (2008). Stochastic resonance in Schottky wrap gate-controlled GaAs nanowire field effect transistors and their networks. Applied Physics Express, 1,083001.

- Kaski, S., & Kohonen, T. (1994). Winner-take-all networks for physiological models of competitive learning. Neural Networks, 7, 973-984

- Kikombo, A.K., Hirose, T., Asai, T., & Amemiya, Y. (2008). Nonlinear phenomena in electronic systems consisting of coupled single-electron oscillators. Chaos, Solitons & Fractals, 37, 100-1007.

- Kim, Y-G., & Kwon, J-K. (2007). Multi-bit Sigma-Delta Modulator for Low Distortion and High-Speed Operation. ETRI Journal, 29, 835-837.

- Likharev, K.K., & Zorin, A.B. (1985). Theory of the Bloch-wave oscillations in small Josephson junctions. J. of Low Temp. Phys., 59, 347-382.

- Mar, D.J., Chow, C.C., W. Gerstner, W., Adams, R.W., & Collins, J.J. (1999), Noise shaping in populations of coupled model neurons. Neurobiology, 96, 1045010455.

- Marculescu, D., & Talpes, E. (2005). Variability and energy awareness: A microarchitecture-level perspective. Proc. of the 42nd annual conf. on Design Automation (DAC), 11-16.

- Mayr, C., & Schueffny, R. (2005). Applying Spiking Neural Nets to Noise Shaping. IEICE - Transactions on Information and Systems, E88-D, 1885-1892.

- Mead, C., (1989). Analog VLSI and neural systems. New York: Addison Wesley.

- Milor, L., & Visvanathan, V. (1989). Detection of catastrophic faults in analog integrated circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 8, 114–130.

- Nikolic, K., Sadek, A., & Forshaw, M. (2001). Architectures for reliable computing with unreliable nanodevices. Proc. of the 2001 1st IEEE IEEE-NANO Nanotechnology conference, 254-259.

- Orshansky, M., Milor, L., Pinhong, C. Keutzer, K., & Chenming, H. (2002). Impact of spatial intrachip gate length variability on the performance of high-speed digital circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 21, 544-553.

- Oya, T., Asai, T., & Amemiya, Y. (2007). Stochastic resonance in an ensemble of single-electron neuromorphic devices and its application to competitive neural networks. Chaos, Solitons & Fractals, 32, 855-861.

- Oya, T., Asai, T., Kagaya, R., Hirose, T., & Amemiya, Y. (2006). Neuronal synchrony detection on single-electron neural network. Chaos, Solitons & Fractals, 27,887-894.

Nakajima, A., Futatsugi, T., Kosemura, K., Fukano, T., & Yokoyama, N. (1997). Room temperature operation of Si single-electron memory with self-aligned floating dot gate. Appl. Phys. Lett., 70, 1742-1744.

Schmid, A., & Leblebici, Y. (2004). Robust circuit and system design methodologies for nanometerscale devices and single-electron transistors. *IEEE* Transactions on Very Large Scale Integration (VLSI) Systems, 12, 1156-1166,.

Schreier, R., & Temes, G.C. (2004). Understanding Delta-Sigma Data Converters. New Jersey: Wiley-IEEE Press.

Shadlen, M.N., & Newsome, W.T. (1998). The Variable Discharge of Cortical Neurons: Implications for Connectivity, Computation, and Information Coding. J. of Neuroscience, 18, 3870-3896.

Shin, J. (2001-a). Adaptation in spiking neurons based on the noise shaping neural coding hypothesis. Neural networks, 14, 907-919.

Shin, J. (2001-b). Adaptive noise shaping neural spike encoding and decoding. Neurocomputing, 38-40, 369-381...

Shint, J.N., Lee, K.R., & Park, S.B. (1993). Novel neural circuits based on stochastic pulse coding and noise feedback pulse coding. Int. J. of Electronics, 74, 359-368.

Simonotto, E., Riani, M., Seife, C., Roberts, M., Twitty J., & Moss, F. (1997). Visual Perception of Stochastic Resonance. Phy. rev. lett., 78, 6, 1186-

Softky, W.R., & Koch, C. (1993). The highly irregular firing of cortical cells is inconsistent with temporal integration of random EPSPs. J. of Neuroscience, 14, 334-350.

Stolk, P.A., Widdershoven, F.P., & Klaassen, D.B.M. (1998). Modeling statistical dopant fluctuations in MOS transistors. IEEE Trans. Electron Devices, 45, 19601971,..

Tiwari, A., Sarangi, S. R., & Torrellas, J. (2007). Recycle: Pipeline adaptation to tolerate process variation. Proc. of the International Symposium on Computer Architecture, 323 - 334.

Utagawa, A., Asai, T., Hirose, T., & Amemiya, Y. (2007). An inhibitory neural network circuit exhibiting noise shaping with subthreshold MOS neuron circuits. IEICE Transactions on Fundamentals of Electronics, Communications and Computer, E90-A, 2108-2115.

Way, K., & Taeho, K. (1999). An overview of manufacturing yield and reliability modeling for semiconductor products. Proc. of the IEEE, 87, 1329-1344.

Andrew Kilinga Kikombo received the BE degree in electronics engineering from the University of Electro-Communications Tokyo, Japan, in 2005 and the MS in electrical engineering from Hokkaido University, Japan, in 2007. He is currently working toward the PhD degree in Electrical engineering at Hokkaido University, Japan. His research interests include modeling, design and simulation of bio-inspired singleelectron circuits. Mr. Kikombo is a member of the Japan Society of Applied Physics.

Tetsuya Asai received the BS and MS degrees in electrical engineering from Tokai University, Kanagawa, Japan, in 1993 and 1996, respectively, and the PhD degree in electrical and electronic engineering from Toyohashi University of Technology, Aichi, Japan, in 1999. He is now an associate professor in the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. His current research interests include nonlinear analog processing in neural networks and reaction-diffusion systems as well as design and applications of neuromorphic VLSIs.

Takahide Oya received the BE, ME, and DrEng degrees in electrical engineering from Hokkaido University, Sapporo, Japan, in 2002, 2004, and 2006, respectively. He is now a lecturer with the Division of Electrical and Computer Engineering, Yokohama National University, Japan. His research interests are

in development of novel nanodevices using carbon nanotubes and designing intelligent electronic circuits with single-electron devices.

Alexandre Schmid received the MS degree in microengineering and the Ph.D. degree in electrical engineering from the Swiss Federal Institute of Technology, Lausanne (EPFL) in 1994 and 2000, respectively. He has been with the EPFL since 1994, working at the Integrated Systems Laboratory as a Research and Teaching Assistant, and at the Electronics Laboratories as a Post-Doctoral Fellow. His earlier work included the development and modeling of high-speed video data compression integrated circuit, CAD for high-performance telecommunication architectures, hardware implementation of artificial neural networks and digital decimation filters for high-speed delta-sigma converters. He joined the Microelectronic Systems Laboratory, EPFL, in 2002 as a Senior Research Associate, where he has been conducting research in the field of nonconventional signal processing hardware and nano-electronic devices. Since 2004, he has also been teaching in the Microengineering Department of EPFL.

Yusuf Leblebici received the BS and MS degrees in electrical engineering from Istanbul Technical University, Istanbul, Turkey, in 1984 and 1986, respectively, and the PhD degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign (UIUC) in 1990. From 1991 and 2001, he served consecutively, as a Faculty Member at UIUC, at the Istanbul Technical University, and at Worcester Polytechnic Institute (WPI), Worcester, MA. Since January 2002, he has been a Full Professor at the Swiss Federal Institute of Technology, Lausanne (EPFL), and director of the Microelectronic Systems Laboratory. His research interests include the design of high-speed CMOS digital and mixed-signal integrated circuits, computer-aided design of VLSI systems, modeling and simulation of nano-electronic circuits, intelligent sensor interfaces, and VLSI reliability analysis.

Yoshihito Amemiya received the BE, ME, and PhD degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 1970, 1972, and 1975, respectively. He joined NTT Musashino Laboratories in 1975, where he worked on the development of silicon process technologies for high-speed logic LSIs. From 1983 to 1993, he was with NTT Atsugi Laboratories and developed bipolar and CMOS circuits for Boolean logic LSIs, neural network LSIs, and cellular automaton LSIs. Since 1993, he has been a Professor with the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. His research interests are in the fields of silicon LSI circuits, signal processing devices based on nonlinear analog computation, logic systems consisting of single-electron circuits, and information processing devices making use of quantum nanostructures.