# Neuromorphic MOS Circuits Exhibiting Precisely Timed Synchronization with Silicon Spiking Neurons and Depressing Synapses

Gessyca Maria Tovar, Tetsuya Hirose, Tetsuya Asai and Yoshihito Amemiya

Graduate School of Information Science and Technology, Hokkaido University Kita 14, Nishi 9, Kita-ku, Sapporo 060-0814, Japan E-mail: gessyca@sapiens-ei.eng.hokudai.ac.jp

Abstract A neural network exhibiting precisely timed synchronization in a noisy environment with depressing synapses was proposed by Fukai and Kanemura [1]. Based on this network, we constructed neural network hard-ware using silicon neurons and depressing synapse circuits and evaluated timing precision among the neurons using a simulation program with integrated circuit emphasis (SPICE). Consequently, timing jitter among the neurons was significantly reduced with depressing synapse circuits compared to nondepressing synapses. Moreover, a novel analog circuit mimicking characteristics of spike-timing dependent plasticity (STDP) was proposed to construct a neural network that exhibits robust synchronization in a noisy environment. We demonstrate the circuit's basic learning characteristics using SPICE.

**Keywords:** neuromophic VLSI, depressing synapse, spiking neuron, recurrent neural network, spike-timing dependent plasticity

## 1. Introduction

Although neurons in the cerebral cortex have firing variations, they often synchronize very precisely [2–4]. The discovery of this synchronous phenomenon was almost concurrent with the appearance of synchronization (clock skew) problems in digital large-scale integrated circuits (LSIs), which are due to the device's parasitic capacitances and resistances. Semiconductor device mismatches have also recently become even more common with the rapid development of sub-micron fabrication processes. Since guaranteeing an appropriate timing margin has so far been difficult, major LSI designers have started using advanced genetic algorithms in post-manufacturing processes to calculate the required margin [5].

Against such a background, reports describing that the population of neurons, each of which has markedly larger variations than present semiconductor devices, exhibits exceptionally accurate synchronization have been extremely inspiring because neurons could provide a possible way to solve the clock skew problem in digital LSIs. A neural network model with depressing synapses that exhibits such precisely timed synchronization even in a noisy environment was recently proposed by Fukai and Kanemura [1]. In this paper we designed analog MOS circuits that 'qualitatively' imitate this network model. The circuit is constructed with silicon neurons and depressing synapse circuits. Using a simulation program with integrated circuit emphasis (SPICE), we demonstrate that depressing synapses facilitate precise synchronization among silicon neurons. Since a higher tolerance to external noises could be achieved by introducing spike-timing dependent plasticity (STDP) learning in the network model [1], we also propose an analog circuit for the STDP learning.

## 2. Precisely Timed Pulse Synchronization Network

Let us briefly review a neural network model for precisely timed synchronization and its dynamic behavior. Then we will introduce two basic MOS circuits that imitate the integrate-and-fire neurons and depressing synapses used in the neural network model.

#### 2.1 Network model

The dynamics of a neural network model for preciselytimed synchronization [1] are given by

$$\tau_m \frac{dV_i}{dt} = -(V_i - V_{\text{rest}}) - \frac{1}{NR} \sum_{j \neq i} c_{ij} g_{ij}^{\text{ee}}(V_i - V_{\text{syn}})$$

$$-g^{\text{ei}}(V_i - V_{\text{cl}}) + E_i$$

$$\tau_e \frac{dE_i}{dt} = -E_i + E_0 \,\delta(t - t_i^{\text{inp}}), \quad (i = 1, \dots, N)$$

$$\tau_i \frac{dV}{dt} = -(V_i - V_{\text{rest}}) - g^{\text{ie}}(V - V_{\text{syn}})$$

where  $V_i$  and V represent the membrane potentials of the *i*-th pyramidal (integrate-and-fire) neuron and an interneuron;  $E_i$  the postsynaptic potential of the *i*-th pyramidal neuron;  $\tau_{m,e,i}$  the time constants of pyramidal neu-

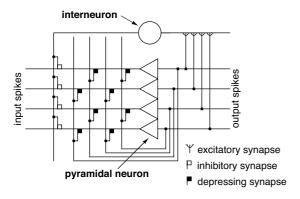

Fig. 1 Neural network model for precisely-timed pulse synchronization

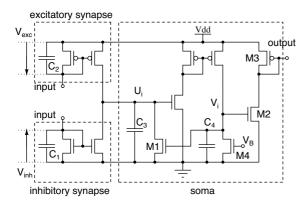

Fig. 2 Silicon neuron with conventional excitatory and inhibitory synapses

rons, excitatory synapses, and interneurons; N the number of pyramidal neurons; R the positive-feedback connectivity between the pyramidal neurons as described below;  $V_{\text{rest,syn,cl}}$  the resting potential of pyramidal neurons, depressing synapse, and interneurons;  $t_i$  the time at which the *i*-th input spike is given;  $c_{ij}$  the binary representing the existence of feedback connections between the *i*-th and *j*-th pyramidal neurons; and  $g^{\text{ee,ei,ie}}$  the synaptic conductance between excitatory-to-excitatory, excitatory-to-inhibitory, and inhibitory-to-excitatory neurons.

Figure 1 illustrates the network model. Four pyramidal neurons (triangles) are shown. All of the outputs of the pyramidal neurons are sent to an interneuron (circle in the figure) through excitatory synapses, whereas the interneuron inhibits all of the pyramidal neurons through inhibitory synapses. Outputs of the pyramidal neurons are randomly connected to pyramidal neurons through depressing synapses (R represents the connection ratio). Since these synapses provide positive feedback connections to pyramidal neurons [1], firing one pyramidal neuron induces firing of other pyramidal neurons. The divergence due to the positive feedback is attenuated by the interneuron that inhibits

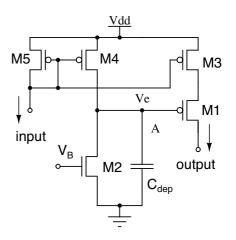

Fig. 3 Depressing synapse circuit

all of the pyramidal neurons.

## 2.2 Silicon neurons and depressing synapse circuits

Asai and Kanazawa *et al.* proposed using silicon neurons and hardware depressing synapses to implement functional spiking neural networks on analog LSIs [6, 7]. We introduce using silicon neurons and depressing synapse circuits to construct the network model described in the preceding subsection and explain the circuit's operational principles.

Figure 2 shows a circuit diagram of a silicon neuron that imitates the basic operations of an integrate-and-fire neuron. Excitatory and inhibitory synapses are constructed by pMOS and nMOS current mirrors that receive input spikes as currents. Delayed synaptic potentials ( $V_{inh}$  and  $V_{\text{exc}}$ ) are generated by capacitors  $C_1$  and  $C_2$ . The excitatory postsynaptic current generated by  $V_{\text{exc}}$  charges  $C_3$ and consequently increases the membrane potential  $U_i$ , whereas the inhibitory postsynaptic current generated by  $V_{\rm inh}$  decreases it. An increase in the membrane potential in the soma circuit induces an increase in potential  $V_i$  by charging  $C_4$ . Thus, when the membrane potential exceeds a certain threshold, the membrane node  $(U_i)$  is suddenly shunted by transistor M1. Although the shunted current increases exponentially with increasing membrane potential, the current is then decreased when  $C_4$  is discharged by M4 with control voltage  $V_{\rm B}$ . This sudden increase and decrease of shunting currents generate a spike. The spike output is obtained by the current of transistor M2 and converted to voltage by the diode-connected transistor M3. For the detailed dynamics and mathematical explanations, see ref. [6].

Figure 3 shows a MOS circuit for a depressing synapse constructed with a *p*MOS current mirror (M3, M4 and M5) and *p*MOS common-source amplifier (M2 and M4). It should be noticed that M4 of the common-source amplifier is shared by the current mirror with M5. When there is no input (current), voltage  $V_e$  at junction A is zero because of a leak current from transistor M2. Therefore, transistor

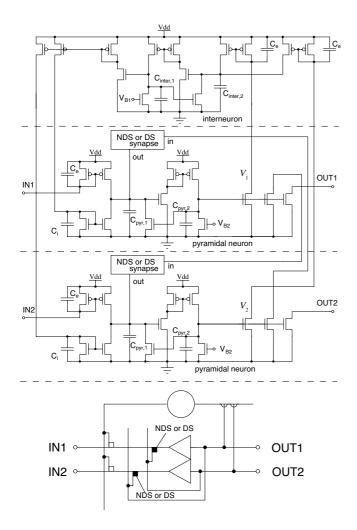

Fig. 4 Circuit diagram of network model with two pyramidal neurons and one interneuron: Each pyramidal neuron circuit has positive feedback connection through nondepressing (NDS) or depressing synapses (DS).

M1 is on. When there is an input current that increases  $V_{\rm e}$ , M1 is turned off. The current is therefore mirrored to output  $I_{out}$  through transistor M<sub>1</sub>. Because there is a parasitic capacitance ( $C_{\rm dep}$ ) at junction A, the increase in  $V_{\rm e}$  has a short time delay. Therefore, M1 is turned on for a short time, and the output current is generated. When the input current becomes zero again, M2 discharges the capacitance  $C_{\rm dep}$ , and  $V_{\rm e}$  returns to zero. Remarkably, the Mirror effect of the pMOS common-source amplifier, which amplifies the value of additional parasitic capacitance between the drain and gate terminal of M4, increases this discharging time. When the spike current is given at a short interval and subsequent spikes enter before  $V_{\rm e}$  returns to zero, the amplitude of the output spikes decreases when  $V_{\rm e}$  increases. Because the current of transistor M2 increases monotonically when  $V_{\rm B}$  increases, the time until  $V_{\rm e}$  returns to zero decreases. Thus by adjusting voltage  $V_{\rm B}$ , the duration of the depression can be changed. Notice that, when  $V_{\rm B}$  is

Fig. 5 Membrane potentials of pyramidal neuron circuits for short time input spike trains through nondepressing (NDS) or depressing synapses (DS)

set to  $V_{dd}$ , the circuit behaves as a nondepressing synapse because  $V_e$  is zero and M1 is always on.

Neural network hardware that is qualitatively equivalent to the network model shown in Fig. 1 is illustrated in Fig. 4. To evaluate basic operations of the network hardware, we used two silicon neurons for pyramidal neurons and one silicon neuron for an interneuron. Outputs of the pyramidal neuron circuits are sent to the interneuron circuit through nondepressing excitatory synapses constructed with pMOS current mirrors, whereas the output of the interneuron circuit is connected to nondepressing inhibitory synapses (nMOS current mirrors) of the pyramidal neuron circuits. Outputs of the pyramidal neuron circuits are also fed back to themselves through nondepressing or depressing synapses, each of which is an excitatory connection. The network accepts external spikes at terminals IN1 and IN2 and produces the output spikes at terminals OUT1 and OUT2.

#### 3. Circuit Simulation Results

We used a simulation program with integrated circuit emphasis (SPICE) to evaluate the proposed circuit with MOSIS parameters (Vendor AMIS, feature size:  $1.5 \ \mu$ m). All the transistor dimensions (channel width and length) were fixed at 2.3 and 1.5  $\mu$ m, except for the channel length of M5 in depressing synapse circuits. To compare the effects of depressing synapses on timing precision of synchronization among pyramidal neurons, we evaluated the network with nondepressing and depressing synapses for feedback connections between pyramidal neurons.

Figure 5 shows membrane potentials of a pyramidal neuron circuit in response to short time burst spike inputs (five spikes with interspike intervals of 500  $\mu$ s) through

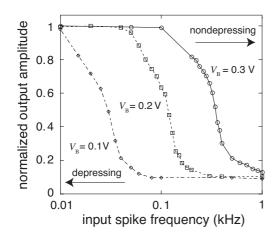

Fig. 6 Changes in amplitude of output of depressing synapse circuit against firing rate of presynaptic neuron

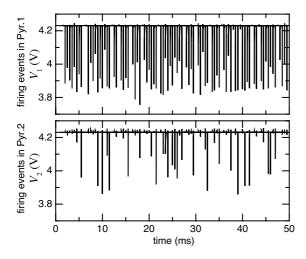

Fig. 7 Output spike trains of pyramidal neuron circuits with nondepressing synapses

nondepressing and depressing synapse circuits. Amplitudes of spike inputs,  $V_{dd}$ ,  $C_{dep}$ , and  $V_B$  were set at 10 nA, 5 V, 100 fF, and 350 mV. The channel length of M5 was set at 3  $\mu$ m for depressing synapses and 6.5  $\mu$ m for nondepressing synapses, which evoked on average the same excitatory postsynaptic potential (EPSP), i.e., charges in membrane capacitances during the burst spike input were fixed to constant values regardless of the type of synapse (nondepressing or depressing). This result ensures that the EPSP generated by the depressing synapse circuit has a larger response at the burst onset than that of the nondepressing synapse circuit. Figure 6 shows the change in amplitude of the output spike against the input firing rate where  $V_{\rm B}$  was set at 0.1, 0.2, and 0.3 V. As the spike frequency increases, the amplitude of the output pulse decreased. By increasing  $V_{\rm B}$ , the cutoff frequency was successfully shifted toward the higher frequency (toward the nondepressing operation).

Based on the extracted parameter results of nondepressing and depressing synapse circuits, we evaluated the

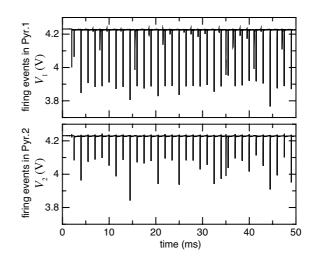

Fig. 8 Output spike trains of pyramidal neuron circuits with depressing synapses

| Table 1 | Comparison of results averaged timing jitters and their  |

|---------|----------------------------------------------------------|

|         | standard deviations ( $\sigma^2$ ) between nondepressing |

|         | (NDS) and depressing synapses (DS)                       |

|                           | NDS  | DS   |

|---------------------------|------|------|

| average jitter ( $\mu$ s) | 0.92 | 0.82 |

| $\sigma^2$ ( $\mu$ s)     | 0.36 | 0.21 |

timing precision of synchronization in the network. In the following simulations, the input spike frequency was fixed at 2 kHz. Capacitance values of  $C_{\text{inter},1}$ ,  $C_{\text{inter},2}$ ,  $C_{\text{pyr},1}$ , and  $C_{\text{pyr},2}$  were set at 1 pF, 100 fF, 300 fF, and 1 pF, whereas capacitors of nondepressing inhibitory and excitatory synapses were removed in this simulation ( $C_i = C_e = 0$ ). The neuron's bias voltages  $V_{\text{B1}}$  and  $V_{\text{B2}}$  were set at 650 and 560 mV. Figures 7 and 8 show output spike trains of pyramidal neuron circuits ( $V_1$  and  $V_2$  in Fig. 4) when nondepressing and depressing synapses were used to connect pyramidal neurons to each other. In both figures, each pyramidal neuron circuit tends to be synchronized in the phase space. For a simple evaluation of the synchronization, we calculated

$$S(t) = H(V_1(t) - \theta) \times H(V_2(t) - \theta)$$

(1)

where  $H(\cdot)$  represents the step function and  $\theta = 4.2$  V. When  $V_1$  and  $V_2$  are fired simultaneously at time t, S(t) becomes 1. Normalizing neuron circuit's intrinsic firing frequency at the ratio of 3  $\mu$ m (depressing) to 6.5  $\mu$ m (nondepressing),  $\sum_{t=0}^{40} {}^{\text{ms}} S(t)$  was 6 for nondepressing whereas it was 17 for depressing synapses, which quantitatively showed an improved synchronization between neuron circuits when depressing synapses were used. We also calculated the timing jitters of output spikes of pyramidal neuron circuits. Table 1 shows a comparison of the results of averaged timing jitters and their standard deviations ( $\sigma^2$ ) between nondepressing and depressing synapses. We found that when depressing synapse circuits were used, the average jitter was 0.1  $\mu$ s better than that of nondepressing synapse circuits. In addition, values of the standard deviation were 60 % better than those of nondepressing synapse circuits. Therefore, we concluded that depressing synapse circuits improve the timing precision of synchronization. Remember that an EPSP generated by a depressing synapse circuit has a larger response at a spike onset than that of a nondepressing synapse circuit (Fig. 5). When nondepressing synapses are used, several spikes are required to evoke enough EPSPs to fire, whereas EPSPs evoked by depressing synapses easily make a pyramidal neuron fire with a few spikes, e.g., even a single spike is sufficient if the threshold potential is set at a very low value. The resultant firing gives rise to the subsequent firing of other pyramidal neurons, which results in fast synchronization among all of the pyramidal neurons.

Synaptic depression is indeed able to detect partial synchrony in the burst times [8]. With nondepressing synapses, the postsynaptic membrane potential follows the presynaptic mean firing rate and is able to be set continuously below the threshold of a neuron. With depressing synapses, however, the partially synchronized bursts push the postsynaptic membrane potential across the threshold repeatedly during stimulus.

# 4. MOS Circuit for STDP Learning

According to the Hebb principle, synapses increase their efficacy if two connected neurons are simultaneously fired. Simultaneous is to be defined by some time window of coincidence. This window of coincidence has being a function of the exact timing of the activity of the presynaptic and postsynaptic neuron, and this phenomenon is called spike-timing-dependent plasticity (STDP). By introducing STDP learning in the original network, Fukai and Kanemura demonstrated that the network exhibited robust synchronization in a noisy environment [1]. In this section, we propose a novel analog circuit emulating the STDP learning. The circuit consists of two basic circuits: a spiketiming detector and an analog memory circuit.

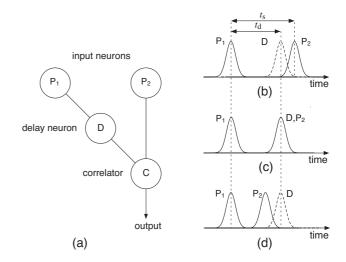

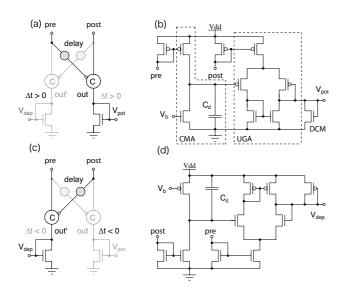

To construct a spike-timing detector, we used a simple correlation neural network [9–11]. Figure 9 shows a local correlation scheme used to account for timing-sensitive responses of output neurons to input spike trains. A primitive correlation neural network consists of two input neurons ( $P_1$  and  $P_2$ ), a delay neuron (D), and a correlator (C), as shown in Fig. 9(a). The arrival of spikes from  $P_1$  at the correlator is delayed by the delay neuron. The output is a correlation value representing the product of delayed and undelayed signals from D and  $P_2$ .

When an input spike is given to  $P_1$  and then to  $P_2$  within the time  $t_s$ , which is longer than the delay time  $t_d$ , the delayed and undelayed signals from D and  $P_2$  do not coincide at the correlator, as shown in Fig. 9(b). If an input spike is given to  $P_1$  and then to  $P_2$  in a time equal to the delay time, the delayed and undelayed signals coincide at the correla-

Fig. 9 Primitive correlation neural network consisting of two input neurons (P<sub>1</sub> and P<sub>2</sub>), delay neuron (D), and correlator (C)

tor [Fig. 9(c)]. Namely, the output signal of the correlator reaches its maximum at the point of coincidence. On the other hand, if an input is given to  $P_1$  and then to  $P_2$  in a time shorter than the delay time, the output signal monotonically decreases as the time decreases [Fig. 9(d)]. Thus, the network can measure the degree of temporal difference by monotonically increasing output signals as the spike intervals between  $P_1$  and  $P_2$  decrease.

Figure 10 show a circuit diagram of spike-timing detectors implementing the correlation neural networks. The circuit consists of a delay circuit (a source-common amplifier and a capacitor), which we denote CMA in Fig. 10(b); a pMOS unity-gain amplifier (UGA); and a current converter (diode-connected MOS transistor DCM). A circuit shown in Figs. 10(a) and (b) detects sequential inputs of pre-to-post spikes. If one spike input is given to terminal pre and then the subsequent spike input is given to terminal **post**  $(t_{\text{post}} - t_{\text{pre}} \equiv \Delta t > 0)$ ,  $V_{\text{pot}}$  increases because input of terminal pre is delayed by the source-common amplifier, while the unity-gain amplifier that accepts the delayed voltage is driven by the post input. Note that the sourcecommon circuit amplifies not only the pre voltage input but also the decay time due to the Miller effect. Since the output of the unity-gain amplifier  $(V_{pot})$  is sent to a diodeconnected nMOS transistor, we can obtain a current output as a result of the current inputs (terminals pre and post). Similarly, Figs. 10(c) and (d) show the inverted circuit of Figs. 10(a) and (b) that detects sequential inputs of postto-pre spikes ( $\Delta t < 0$ ).

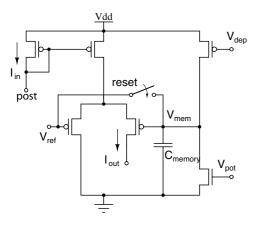

An analog memory circuit for STDP learning is illustrated in Fig. 11. The circuit consists of a *p*MOS differential pair, a storage capacitor ( $C_{\text{memory}}$ ), and *p*MOS and *n*MOS current sources that receive the output of spiketiming detectors ( $V_{\text{pot}}$  and  $V_{\text{dep}}$ ) constructing *p*MOS and *n*MOS current mirrors. The storage capacitor is dis-

Fig. 10 Spike-timing detectors

Fig. 11 Analog memory circuit for weight storage

charged (or charged) by pre-to-post (or post-to-pre) input spikes through  $V_{\rm pot}$  (or  $V_{\rm dep}$ ), e.g., when  $\Delta t > 0$ ,  $V_{\rm pot}$ is increased and thus the storage capacitor is discharged. Synaptic weight strength w between pre and post neurons is defined by the ratio of input current  $I_{\rm in}$  to output current  $I_{\rm out}$  and controlled by the difference between capacitor voltage  $V_{\rm mem}$  and reference voltage  $V_{\rm ref}$ . Initially  $V_{\rm mem}$ is set to  $V_{\rm ref}$  by manual reset switching, i.e.,  $I_{\rm out} = I_{\rm in}/2$ and thus w = 2. When all the transistors operate in their subthreshold regions, weight strength w is given by

$$w = \frac{I_{\rm in}}{I_{\rm out}} = \frac{1}{f(V_{\rm mem} - V_{\rm ref})}$$

$$\left[f(x) = \frac{1}{1 + \exp(-\kappa x/V_T)}\right]$$

where  $\kappa$  represents the effectiveness of the gate potential, and  $V_T \equiv kT/q \approx 26$  mV at room temperature (k is Boltzmann's constant, T the temperature, and q the electron charge) [12, 13].

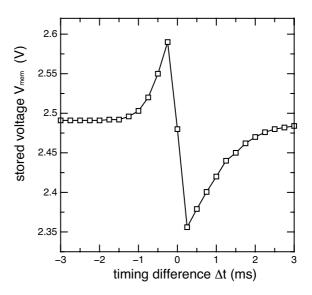

Fig. 12 Simulation results of STDP circuit

Figure 12 shows simulation results of the proposed STDP circuit. The horizontal and vertical axes represent  $t_{\text{post}} - t_{\text{pre}} (\Delta t)$  and capacitor voltage  $V_{\text{mem}}$ . The powersupply and reference voltages were set at 5 and 2.5 V. The memory capacitance value was set at 500 fF. As expected, the circuit mimicked basic characteristics of STDP learning; however, the asymmetry characteristic was observed. This is simply due to the unbalanced saturating properties of *p*MOS and *n*MOS current sources in Fig. 11, which could be improved by using relatively long channels for the current sources.

# 5. Conclusion

We designed a neural network circuit to demonstrate precisely timed synchronization among silicon neurons with depressing synapse circuits. The network circuit was designed using popular metal-oxide-semiconductor (MOS) devices. The key to synchronizing neurons precisely was introducing positive feedback to the neurons and using depressing synapses instead of nondepressing (conventional) synapses for the feedback connections. Consequently, in our demonstration assuming a  $1.5-\mu$ m CMOS process, precision was improved by 60% when depressing synapse circuits were used instead of nondepressing synapses. Furthermore, we designed a novel synapse circuit that qualitatively mimics spike-timing dependent plasticity (STDP) learning characteristics. By circuit simulations, we demonstrated the learning characteristics.

## Acknowledgments

This study was supported in part by the Industrial Technology Research Grant Program in 2004 from the New Energy and Industrial Technology Development Organization (NEDO) of Japan and by a grant-in-aid for young scientists [(B)17760269] from the Ministry of Education, Culture, Sports, Science, and Technology (MEXT) of Japan.

# References

- T. Fukai and S. Kanemura: Noise-tolerant stimulus discrimination by synchronization with depressing synapses, Biol. Cybern. Vol. 85, No. 2, pp. 107–116, 2001.

- [2] P. Fries, P.R. Roelfsema, A.K. Engle, P. Konig and W. Singer: Synchronization of oscillatory responses in visual cortex correlates with perception in interocular rivalry, Proc. Natl. Acad. Sci. USA, Vol. 94, No. 23, pp. 12699– 12704, 1997.

- [3] A. Riehel, S. Grun, M. Diesmann and A. Aersen: Spike synchronization and rate modulation differentially involved in motor cortical function, Science, Vol. 278, pp. 1950–1953, 1997.

- [4] Y. Dan, J-M. Alonso, W.M. Usrey and R.C. Reid: Coding of visual information by precisely correlated spikes in the lateral geniculate nucleus, Nature Neurosci., Vol. 1, No. 6, pp. 501–507, 1998.

- [5] E. Takahashi, Y. Kasai, M. Murakawa and T. Higuchi: A post-silicon clock timing adjustment using genetic algorithms, Digest of Technical Papers: 2003 Symposium on VLSI Circuits, Vol. 12-14, pp. 13–16, 2003.

- [6] T. Asai, Y. Kanazawa and Y. Amemiya: A subthreshold MOS neuron circuit based on the Volterra system, IEEE Trans. Neural Network, Vol. 14, No. 5, pp. 1308–1312, 2003.

- [7] Y. Kanazawa, T. Asai, M. Ikebe and Y. Amemiya: A novel CMOS circuit for depressing synapse and its application to contrast-invariant pattern classification and synchrony detection, Int. J. Robotics and Automation, Vol. 19, No. 4, pp. 206–212, 2004.

- [8] W. Senn, I. Segev and M. Tsodyks: Reading neuronal synchrony with depressing synapses, Neural Computation, Vol. 10, No. 4, pp. 815–819, 1998.

- [9] W. Reichardt: Principles of Sensory Communication. Wiley, New York, 1961.

- [10] D.C. Carroll, N.J. Bidwell, S.B. Laughlin and E.J. Warrant: Insect motion detectors matched to visual ecology, Nature, Vol. 382, pp. 63–66, 1996.

- [11] R. Kern, M. Egelhaaf and M.V. Srinivasan: Edge detection by landing honeybees: behavioural analysis and model simulations of the underlying mechanism, Vision Res., Vol. 37, pp. 2103–2117, 1997.

- [12] A.G. Andreou, K.A. Boahen, P.O. Pouliquen, A. Pavasović, R.E. Jenkins and K. Strohbehn: Current-mode subthreshold MOS circuits for analog VLSI neural systems, IEEE Trans. Neural Networks, Vol. 2, No. 2, pp. 205–213, 1991.

- [13] E.A. Vittoz: Micropower techniques, in Design of MOS VLSI Circuits for Telecommunications, Y. Tsividis and P. Antognetti, Eds., Prentice-Hall, Englewood Cliffs, NJ, pp. 104–144, 1985.

Gessyca Tovar was born in Venezuela in 1981. She received the B.S. degree in Electronic Engineering from Jose Antonio Paez University, Venezuela, in 2004. She is currently working towards her Master degree at Hokkaido University, Japan. Her research interests include neuromorphic computation and hardware implementation.

**Testuya Hirose** received the B.S., M.S. and Ph.D. degrees from Osaka University, Osaka, Japan, in 2000, 2002, and 2005, respectively. Currently, he is a Research Associate in the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. His current research interests are in low-power analog/digital CMOS circuits and subthreshold MOS-FET functional circuits for intelligent sensors. Dr. Hirose is a member of the Institute of Electronics, Information and Communication Engineers of Japan, and the

IEEE.

Tetsuya Asai is an Associate Professor in the Graduate School of Information Science and Technology, Hokkaido University, Sapporo, Japan. His research interests concentrate around developing nature-inspired integrated circuits and their computational applications. Current topics that he is involved with include; intelligent image sensors that incorporate biological visual systems or cellular automata in the chip, neuro chips that implement neural elements (neurons, synapses, etc.) and neu-

romorphic networks, and reaction-diffusion chips that imitate vital chemical systems.

> Yoshihito Amemiya received the B.E., M.E., and Ph.D. degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 1970, 1972, and 1975. He joined NTT Musashino Laboratories in 1975, where he worked on the development of silicon process technologies for highspeed logic LSIs. From 1983 to 1993, he was with NTT Atsugi Laboratories and developed bipolar and CMOS circuits for Boolean logic LSIs, neural network LSIs, and cellular automaton LSIs. Since 1993, he has been a Professor in the Department

of Electrical Engineering, Hokkaido University, Sapporo. His research interests are in the fields of silicon LSI circuits, signal processing devices based on nonlinear analog computation, logic systems consisting of single-electron circuits, and information-processing devices making use of quantum nanostructures.

(Received May 29, 2006; reviced August 8, 2006)