# 単電子デバイス・回路の研究状況と今後の展望

俊郎\*\*\* 道晴\* 俊理\*\* 田部 小田 和郎\*\*\*\*

ひとつひとつのの電子の動きを制御する、単電子デバイスと呼ばれる新しい概念が産声をあげて約 1○年が経った、この間、「単電子」を頭に冠するトランジスタ、メモリー、論理回路などさまざまな デバイス・回路が急ピッチで試作され,単電子物理に根差した独特の振舞が次々と実証されている.さ らに、単電子に適した新しい回路や情報処理手法の研究も進展している.一方で、将来の集積化を念頭 に置いたさまざまな課題も浮き彫りにされつつある.ここでは、デバイス応用の立場から、単電子に関 わる研究状況と今後の展望について述べる.

Keywords: single-electron, single-electron device, single-electron circuit, single-electron transistor, single-electron memory, Coulomb blockade of tunneling

# 1. まえがき

電子1個1個のトンネル移動を制御する単電子デバイス とその物理は、1950年代から約30年にわたる黎明期を経 て、1980 年代半ばに Likharev らの一連の研究<sup>1)</sup> によって 幕が開いた。単電子デバイスは、通常いくつかの微小トン ネル接合とマクロな回路素子からなっており, その原理は 「クーロンブロッケード」と呼ばれる電子トンネリングを 阻止する機構に基づいている。微小な(十分小さな容量 C をもつ) 平行平板電極で挟まれたトンネル接合では, 電子 が電極間をトンネル移動する際, たとえ電子1個のトンネ リングであっても接合の静電エネルギー Q²/2C (Q は接 合の蓄積電荷)の変化が背景熱エネルギーに比べて大きく なり、ある電荷範囲ではトンネリングが静電エネルギーの 増加をもたらすため禁止される (クーロンブロッケード)。 このように原理は単純であるが、単一接合でこの現象を観 測することは困難を極め, 実際には小さな中央電極 (ノー ド)の左右にトンネル接合をもつ2重接合構造ではじめて 実験が進展した。これは、注目している接合と外部回路を 切り離して考えることができず、接合から見た外部インピ ーダンスの影響が本質的に重要であることを意味してい る2).

今日単電子に関わる研究は,基礎物理,デバイス,回路 アーキテクチャにわたる裾野の広がりをみせており、次第 に半導体技術者の注目を集めはじめている。 その理由は, いくつかある。第一は、基本原理が電子の波動干渉性によ るものでなく粒子的描像に根ざしているため, 多様なデバ イスや回路を考案することが比較的容易であること、第二 は、1992年頃までに単電子独特の振舞が次々に実証され ていったこと(トランジスタ3),ターンスタイル4),ポン プ5)など),第三に、少数の電子の動きを利用しているた め超低消費電力という実用上の利点が明白であり、今日の LSIが抱える問題点を解決する方向にベクトルが向いてい ることである。材料面で見てみれば、当初は Al など金属 が主体であったが、その後半導体にシフトして GaAs 系 が中心となり、さらに最近では、Si も用いられるように なってきた.

単電子デバイスの研究は, 単電子の基本動作を調べる段 階から新たな一歩が踏み出されようとしている。それは、 実用に向けての第一歩として、これまで極低温に限られて いた単電子トランジスタの動作温度を室温にまで高める研 究6~9) や,メモリー,論理回路などその具体的な応用回 路10~12,24)の実証的研究が本格化してきたことである。さ らに、量子ドットを敷き詰めた構造を内部配線不要なセル

分類番号 3.7, 3.8

Present status and future prospects of single-electron devices and circuits. Michiharu TABE\*, Shunri ODA\*\*, Toshiro HIRAMOTO\*\*\*, Kazuo NAKAZATO\*\*\*\* and Yoshihito AMEMIYA†.

<sup>\*</sup> 静岡大学電子工学研究所 〒 432 浜松市城北 3-5-1.

<sup>\*\*</sup> 東京工業大学量子効果エレクトロニクス研究センター 〒 152 東京都目黒区大岡山 2-12-1。

<sup>\*\*\*</sup> 東京大学生産技術研究所第3部 〒106 東京都港区六本木7-22-1.

<sup>\*\*\*\*</sup> 日立ケンブリッジ研究所。

北海道大学工学部電子工学科 〒060 札幌市北区北13条西8丁目。

Research Institute of Electronics, Shizuoka University (3-5-1 Johoku, Hamamatsu 432)

<sup>\*\*</sup> Research Center for Quantum Effect Electronics, Tokyo Institute of Technology (O-okayama, Meguro-ku, Tokyo 152)

<sup>\*\*\*</sup> Institute of Industrial Science, University of Tokyo (7-22-1 Roppongi, Minato-ku, Tokyo 106)

<sup>\*\*\*\*</sup> Hitachi Cambridge Laboratory, Microelectronics Research Centre, Cavendish Laboratory (Madingley Road, Cambridge, CB3 0HE, U. K.)

Fuculty of Engineering, Hokkaido University (Kita 13, Nishi 8, Kita-ku, Sapporo-shi 060)

オートマトンに応用する<sup>13)</sup> など新しい回路アーキテクチャの提案もされている。一方で,まだまだ未開拓の単電子物理を発掘する基礎的研究も進展しており,対称性のよい量子ドットがもつドット内電子の殻構造<sup>14)</sup>,単電子トランジスタへの光照射の効果<sup>15)</sup>,複数の量子ドットのカップリング効果<sup>16,17)</sup>,など興味深い現象が次々と報告されている。

しかし、遠い将来から眼を転じて実用デバイスの観点から眺めれば、ノードごとにばらつきをもつオフセット電荷や狭い動作マージンなど単電子デバイス固有の問題点も山積している。本報告では、まず基本原理を簡単に述べた後、デバイス応用の立場から最近の研究動向と課題について述べる。

#### 2. クーロンブロッケード

ここでは、単電子デバイスを理解する上で重要な基本原理を要約する。より詳しくは、文献1),2)などを参照されたい。

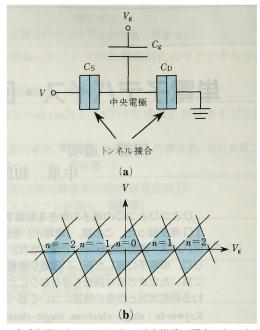

クーロンブロッケードは、単一トンネル接合で簡単に説 明されるが、実験的検証やデバイス研究はもっぱら2重 (または多重)接合で行われてきた。その理由は、外部回 路が量子抵抗  $(h/e^2=25.8k\Omega)$  より大きな抵抗を持つこ とがクーロンブロッケード観測のひとつの条件であり、こ れを満足させることが実験的には極めて困難であることに よる。現実の回路で実現容易な定電圧源を接続した場合, 外部抵抗が小さいと単電子トンネルが生じても瞬時に接合 に電荷が供給され、結局個々のトンネリングが無相関に起 こるためである。定電圧源と接続された2重接合では、片 方のトンネル抵抗が大きな外部抵抗の役目を果たし、クー ロンブロッケードの観測条件を満たすことが容易である. この2重接合は、図1(a)のように、中央電極(ノード) に容量 Cg を介してゲート電極端子を設ければ直ちにトラ ンジスタ構造となる. この場合, ノード内の正味電荷を Qとすれば (Qは常に素電荷の整数倍), ノードの静電エ ネルギーは  $Q^2/2C_{\Sigma}$  (ただし  $C_{\Sigma}$  は中央の微小領域からみ た全容量)で表される.

この構造でクーロンブロッケードが起こる条件は,系の 静電エネルギーの計算から図1(b)のようにバイアス電圧 vs. ゲート電圧平面で菱形領域となる。すなわち、バイア ス電圧 V が低いところ  $(|V| < V_c = e/C_{\Sigma})$  では,ノ ード内の電子数はある整数値に固定されたままでクーロン ブロッケードにより電流が流れない。 さらに Vを大きく していくと, 両接合のクーロンブロッケード条件が順次破 れて電流が流れ始め、2つの接合容量と抵抗にアンバラン スがあれば、電流は電圧の関数として階段的に増加する (クーロンステアケース)。一方,ゲート電圧に対しては, 電流は周期 e/Cg で振動 (クーロンブロッケード振動) し、ゲート電圧は電流のスイッチング機能をもつ。すなわ ち、ゲート電圧の増加とともに、ノード内電子数が1個ず つ増えた状態でクーロンブロッケードが働き, 電子数の切 り替わり電圧領域で周期的にクーロンブロッケード条件が 破れて電流ピークが生じる。言い換えれば、1つのピーク

図 1 (a)単電子トランジスタの基本構造、図中のトンネル接合の記号は、慣用的に用いられているものである。 (b)クーロンブロッケード領域 (網かけ部分). 各網かけ領域では、両接合ともトンネリングは禁止され電流は流れない、Vを小さな値に設定しておいて  $V_8$ を変化させるとノード内電子数 n は 1 つずつ増加する。

を越えるごとにノードに蓄積されている電子数が1個ずつ 増加する。これらが、単電子トランジスタの基本特性であ る

これらの特性を熱雑音に打ち勝って観測・応用するに は、ゲート容量まで含めた中央電極から見た全容量  $C_{z}$  を 十分に小さくする必要がある.たとえば,Czを10<sup>-18</sup>F (aF)まで小さくすれば、室温でクーロンブロッケードを 利用することも可能となるが、1つのトンネル接合で見た 場合極板間隔を1nmとすれば極板の大きさを数nm□の オーダまで抑え込む必要がある。そのためには、ノード部 をドット (微小島) と呼ばれるほど小さくする必要がある が、ここで注意しておく問題がある。通常障壁で囲まれた ドット内では程度の差こそあれ電子準位が量子化してしま う(量子ドット)。単電子デバイスの動作においては、電 子トンネリングは静電エネルギーで決まることが基本であ り、電子準位の量子化は特性を複雑にし、また素子間ばら つきを増大させる要因になる.さらに,ドットが小さいと 2 重接合を電子が共鳴的にトンネルしてしまう現象 (共鳴 トンネリング) も予想される。単電子デバイスでは、電子 トンネリングは非共鳴的に(1 つの接合ごとに独立に)生 じることが必要であり,ノード内に飛び込んできた電子は 十分な非弾性散乱を受けることが望ましい。 このように, 構造の微細化にともなって現われる「迷惑な量子効果」を いかに取り除くか,または何らかの発想で積極的に利用で きるか、が今後の課題である。また、単電子トランジスタ の回路応用では、ほとんどの場合、クーロンブロッケード 振動によるゲート電圧の電流スイッチング機能を用いる。 ここで、単電子トランジスタの電圧ゲインは  $C_{\rm g}/C_{\rm D}$  ( $C_{\rm D}$ はドレイン側の接合容量) で与えられるため、高温動作を

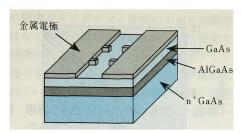

図2 GaAs 二次元電子ガスと微小突起を持つゲート電極に よるクーロンアイランドの形成. (文献21)より転載.)

狙ってゲート容量だけを小さくするとゲインが低下し,回 路特性が劣化する恐れがある。したがって,微細化にあたっては各容量をバランスよく減少させる必要がある。

# 3. 単電子トランジスタの各種作製法とその特性

#### 3.1 単電子トランジスタの研究経緯

上に述べたように、室温動作デバイス実現のためには数 nm 程度の寸法を作らなければならない。PMMA などのレジストを利用する電子ビーム露光技術で得られる最小寸法はせいぜい 20 nm である。このリソグラフィ技術の限界と微細構造形成の要求のギャップを埋めるためにさまざまな工夫がなされてきた。

単電子トンネル現象そのものは今から 45 年も前に金属 微粒子中にいわば偶然にできた構造の電気伝導の異常として観測されているが<sup>18</sup>, リソグラフィ技術を用いて構造の制御された微小トンネル接合を形成し単電子トランジスタ 特性を観測したのは、Fulton と Dolan が最初である<sup>3)</sup>。 斜方蒸着とリフトオフ技術を特徴とする彼らの方法は多重接合の作製が可能であり、文献 19)に詳述されている。この方法を応用して AI/AIO<sub>x</sub>/AI 微細接合を形成しメモリーセルの動作が確認されている<sup>20)</sup>。

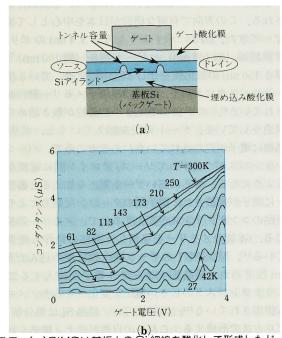

その後, 化合物半導体へテロ接合の二次元電子ガスとゲ ート電極のパターニングにより形成された量子ドット構造 の研究21~23)が、盛んに行われてきた。図2に示すデバイ ス構造<sup>21)</sup>において、n<sup>+</sup>GaAs 基板に加える下部ゲート電 圧を調節することにより GaAs/AlGaAs 界面に形成され る二次元電子ガスの電子濃度を制御する。上部 GaAs 表 面に設けた1対の金属ゲート電極に負バイアスを加えるこ とにより、電極直下には空乏層を発生させ、一次元電子チ ャネルを形成する。1対の電極の間隔は450 nm 程度であ るが、実際に電界により閉じこめられたチャネルの幅はず っと狭くなる。ここで重要なのは上部ゲート金属に設けた 2個ずつの突起であり、一次元電子チャネルに対してポテ ンシャル障壁として働くので,中間部にはノード(導電性 アイランド)が形成される。2箇所の突起の間隔は0.5~1 μm 程度であるが,希釈冷凍機を使用して 50 mK 程度に 冷却した試料では、チャネルのコンダクタンスが下部ゲー ト電圧によって変調されるクーロンブロッケード現象を観 測することができる。この空乏層ポテンシャルを利用した 方法は、電圧によって障壁高さやノードのサイズを制御で きるという特徴があり優れた方法であるが、高温動作への 見通しは明るくない.

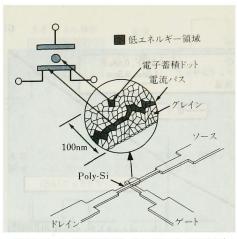

図3 ポリシリコン超薄膜微細トランジスタ (文献 6)より転載).

#### 3.2 単電子トランジスタ動作の高温化

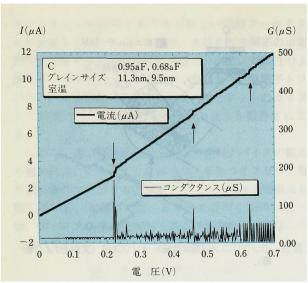

単電子デバイスを実用化するためには, 室温動作が要求 される。この方向で有望な研究が日本を中心として盛んに なってきた。図3に示すような厚さ3.4 nm のポリ Si 超 薄膜細線(幅100 nm)とゲート電極(幅100 nm)とが, 厚さ 150 nm の酸化膜を介して互いに交差している構造の トランジスタにおいて,室温で単電子メモリー動作が確認 されている6、ポリSi は数 nm の結晶粒が敷き詰められた 構造をしている。ゲート電圧を加えていくと、ポリ Si 結 晶粒に電子が充たされていき, あるところで, パーコレー ションパスがつながってソース/ドレイン間に電流が流れ るようになる。 さらに高いゲート電圧を加えると蓄積ドッ トに電子が捕獲され、電子間のクーロン反発力により電流 経路のコンダクタンスが変化するので,メモリー効果を生 じる。64個のメモリーを集積した回路の動作も発表され ている<sup>24)</sup>。MOSFET のゲート酸化膜に埋め込んだ粒径 5 nm 程度のナノ結晶 Si にチャネル電子を注入することに よりトランジスタのしきい電圧を変化させるナノメモリー も提案されている<sup>25)</sup>。半球状のナノ結晶 Si は熱分解 CVD プロセスで形成する。これらの自然形成ナノ構造を利用す るデバイスの今後の課題は、結晶粒の大きさを揃えること により, しきい電圧などの特性を一定にすることである. この方向の研究として、最近シランと水素のパルスプラズ マプロセスにより粒径 8±1 nm の単分散 Si 量子ドットを 形成し、室温で擬一次元 Si ドットアレーに基づくクーロ ン階段状の電気特性(図4)が観測されている26)。

Si は,熱酸化を利用することによってリソグラフィー限界を越える微細構造が形成できるという材料的メリットがあるが,1つのアイランドからなる最も単純な単電子トランジスタを作ることは意外にむずかしい。Si で1つのアイランドをもつ高温動作の単電子トランジスタは,SOI (Silicon on Insulator) の1種である SIMOX (Separation by Implated Oxygen) 基板を用いて実現された $^{70}$ . すなわち,厚さ 30 nm の上部 Si 層を電子ビーム露光により,長さ 50 nm,幅 30 nm に加工し,さらに酸化処理を行うことにより数 nm オーダーの Si 微細構造を作製したが,このとき酸化速度のパターン依存性を巧みに利用して

図 4 擬一次元 Si ドットアレーの室温における電流ー電圧特性<sup>26</sup>. 電極間の距離は 26 nm である.

(b)

図5 (a)SIMOX 基板上の Si 細線を酸化して形成したドットを用いた単電子トランジスタの模式図. (b)電流のゲート電圧依存性 (文献 7)より転載).

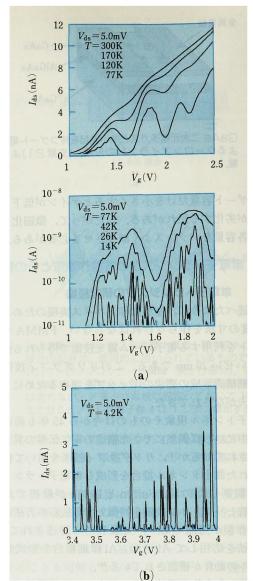

Si 細線の両端部にくびれを作り、Si アイランドを形成している。図5(a)は、このようにして作製した単電子トランジスタの模式図である。図5(b)は、この単電子トランジスタの電流ーゲート電圧特性である。低温では、周期的なクーロンブロッケード振動が明瞭に観測されている。この周期から、ゲート容量 $C_g$ は約0.3aFと求められる。一方、温度が上昇すると、クーロンブロッケード振動の振幅は徐々に小さくなるが、室温においても振動が残っている。微小ドットの全容量は、約2.3aFと見積もられている。微小ドットの全容量は、約2.3aFと見積もられている。類似の方法を用いて、チャネルの脇にサテライトアイランドを作り、メモリー機能を見出した報告もある $2^{20}$ 。しかし、この作製法も、トンネル接合となるくびれ部分の構造やポテンシャル形状に不明な点が多く、今後さらなる解明が必要である。

図 6 (a)SIMOX 基板上で異万性エッチングと選択酸化を 用いて形成した MOS 細線から得られた単電子トラン ジスタの特性 (b)4.2 K での特性 マルチドット系 の特徴が現われている (文献 8)より転載).

複数ドットをもつ高温動作単電子トランジスタの例とし て、SIMOX 基板上で Si の異方性ウエットエッチングと 選択酸化技術を応用して MOS 細線を形成する試みがあ る<sup>8)</sup>. 図 **6(a)**は,作製した Si 単電子トランジスタの特性 である8. このデバイスの場合は、細線部の長さが比較的 長い(100 nm) ため, 微小領域が1つではなく、細線中 に複数の量子ドットが直列に接続されていると考えられ る。77 K以上では明瞭なクーロンブロッケード振動が観 測されるが、77K以下では、この大きな振動が細かいピ ークに分裂している. 4.2 K では, 図 6(b)に示したよう に、非常に鋭いピークが観測され、そのピーク高さが変調 されていることがわかる. これは、マルチドット系の特徴 で28)、複数の量子ドットが弱くカップリングすることによ り形成されたエネルギーレベルを反映していると考えられ る29)。これと類似の方法として、極薄 SOI の側壁部に極 薄酸化膜を形成した後ポリシリコンゲートを堆積し, MOS 細線を形成した報告もある30)。これらの方法は、微 細構造の形成をリソグラフィ技術の平面寸法精度に依存するのではなく制御の容易な膜厚方向の寸法精度を利用することに特徴があるが、構造(したがってポテンシャル)の微妙な揺らぎにより、0次元量子構造の多重接合が自然に形成されている。ドット構造の制御が今後の課題である。

# 3.3 単電子トランジスタの課題——協調トンネリングとオフセット電荷——

単電子トランジスタの動作限界を決める要因の一つに, 協調トンネリング (co-tunneling) とよばれる現象があ る31)。これは、2つ以上の接合を電子が同時にトンネルす る現象のことで,図5,6で見られるようにクーロンブロ ッケード領域の漏れ電流となる。協調トンネリングを抑え るには、2つの接合のトンネル抵抗を大きくするか、また は接合の数を増やせばよい。今後,応答スピードの劣化を 防ぎながら漏れ電流を抑える工夫が必要となる。また、別 の課題として、熱サイクルによる特性変動およびオフセッ ト電荷の問題がある。ドットの近辺には、常に可動電荷や 固定電荷が存在する可能性がある。これまでの単電子トラ ンジスタでは, 低温測定, 室温戻し, の熱サイクルによっ て、あるいは同一温度での測定中においても電荷の移動に より特性が変動することが知られていた。Siでは、SiO2 との界面が良好であるために、このような変動がないこと が報告されているが32)、オフセット電荷の有無とそれによ るデバイスごとの特性ばらつきの問題は手がついていな い。ランダムなデバイス特性ばらつきを自己的に補償する ような、新しい回路アーキテクチャが必要となるかもしれ ない.

# 3.4 その他の作製法と構造

微小接合を作る他の手法として、走査プローブ顕微鏡技術を用いたものがあり、原子・分子レベルでの材料修飾が盛んに行われている。大気中で原子間力顕微鏡の導電性探針と試料間に電圧を加えて Ti や Nb の表面微細領域を酸化してクーロンアイランドを形成した報告<sup>9)</sup> や超高真空環境で STM を用いて、Si 表面を被覆している水素原子を局所的に離脱させた後に酸化や金属の選択的 CVD を行う水素原子レジストプロセスの報告<sup>33)</sup> がある。

また、結晶方位の揃った Si ドットの二次元配列を狙って Si 表面の高密度熱窒化核をマスクとする選択酸化プロセスを用いた方法も提案されている $^{34}$ . さらに、理論検討の段階であるが、新しい構造として、トンネル接合特性に方向性を持たせて使いやすい回路素子を作ろうとする提案がある $^{35,36}$ .  $^{2}$  層構造の障壁を用いてトンネルコンダクタンスの順逆比  $^{10^5}$  が予測されている $^{36}$ .

#### 4. 単電子デバイスによる電子回路の構成

以上述べてきたような個別単電子デバイス(特にトランジスタ)の研究と並行して、単電子デバイスの集積化を念頭に置いた回路の研究も活発に行われている。単電子デバイスによる LSI には2つの目的がある。既存 LSI の限界を越える高集積・低電力化を実現すること、および電子の個別性を巧みに利用して新しい機能を実現することである。以下に、将来の単電子 LSI に向けた基本技術となる

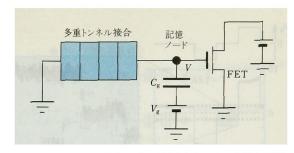

図7 多重トンネル接合による単電子メモリーの基本回路. 記憶ノードの電位 V を FET で検出する.

図8 ゲート電圧 V<sub>8</sub> より, クーロンブロッケード領域中の任意の電子状態を2つの状態に移すことができる.

単電子デジタル回路の研究例を紹介する。なお、CMOS LSIの開発ではプロセスとシミュレーションが互いに補完的な役割を果たしている。単電子回路でも状況は同じであるが、プロセスが未完成な分だけシミュレーションの役割が重くなる。現在では、電荷平衡解析とモンテカルロ法を組み合わせたシミュレーション手法³¹¹ が一般に使われている。なお、半導体に特徴的なバンドベンデイングの効果などをシミュレーションに取り入れることが今後の課題である。

#### 4.1 単電子メモリー

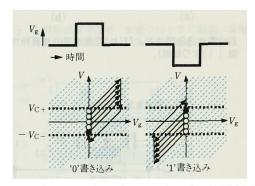

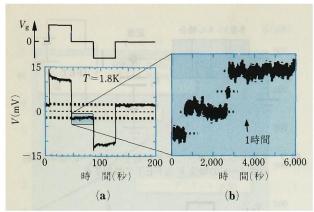

単電子メモリの基本動作は, ビット情報を担う電子をク ーロンブロッケードで保持することにある<sup>28,38~41)</sup>。基本 回路の一例を図7に示す。複数のトンネル接合を直列接続 した多重トンネル接合の片側に記憶ノードをつなぎ, その 記憶ノードには書き込み用のキャパシタ  $C_{g}$  と電源  $V_{g}$ , 読み出し用の FET を接続する。多重トンネル接合は有限 のクーロンブロッケード領域  $-V_{c-} < V < V_{c+}$  をもつので、 図8のように電圧  $V_{\rm g}$ を振ることで記憶ノードの電位を  $V_{c+}$ と  $-V_{c-}$ の2つの状態に変えることができる。これに よって情報の1ビット, '1' および '0' ビットを記録する。 図の点線は記憶ノードにおける電子数が一定の条件,  $C_{\Sigma}V = C_{g}V_{g} - en$  (n は記憶ノードの過剰電子数で整数 値)を表している。ゲート電圧 Vg により電子の状態がク ーロンブロッケード領域の外に移されると,多重トンネル 接合を通して電子の移動が起こり, 再びクーロンブロッケ ード領域内に電子の状態が落ち着く。

図9は実験回路による書き込み読み出し特性である $^{11}$ . ゲート電圧  $V_g=0$  で異なる2つの状態が保持される。情報書き込み後に電子が1 個ずつ抜けることにより記憶が失われていくが,その時間スケールをみると本例では1時間

図9 (a)書き込み特性および(b)記憶情報の減衰特性(文献11)より転載).

図 10 集積メモリーセル構造. 記憶ノードへの電子注入を (a)チャネル側からする方法と(b)ゲート側からする方法.

図11 CMOS型単電子論理回路44~46).

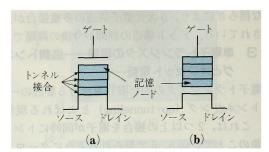

のオーダーである。実用化には、高集積が可能なデバイス構造を工夫する必要がある。図 10(a)はその一例であり、多重トンネル接合と FET のチャンネルを一体化する。この構造は従来のフラッシュメモリーの延長線上にある。実験的に室温動作が得られており、ROM への応用が期待できる<sup>24,25,42)</sup>。高速 RAM を構成する場合には、図 10(a)の構成では読み出し時間と書き込み/消去時間の最適化が困難で、図 10(b)のように、多重トンネル接合と FET のゲート電極を一体化する構造の方が優位である。いずれの構造においても、実用に向けた研究が進められている。

# 4.2 単電子による論理回路

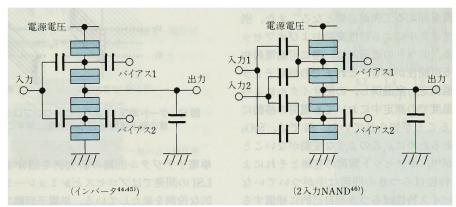

#### 4.2. ] CMOS 類似の論理ゲート回路

単電子の論理ゲート回路として当初考えられたものは、既存トランジスタをそのまま単電子トランジスタに置き換えた形の回路であった<sup>43)</sup>。しかし単電子トランジスタに持続電流を流すので消費電力が大であり、また電流を微小にすると誤動作が多くて現実的ではない。

そこで、電流のかわりに島ノードの電子個数を制御して出力電圧を変化させる方式が提案された。この考え方が現在の主流になっている。図11の回路⁴⁴~⁴⁶)はその代表例であり、Si CMOS に類似の回路を単電子トランジスタで構成している。この回路はCMOS と同じくスタンバイ電力が 0 である。電流ではなく電位を基本に置いており、電子数が少なくても動作できる。ただし、確率ゆらぎを抑えて安定な動作を得るため、積極的に 10 個以上の複数電子を

使う設計思想もある<sup>46)</sup>。また、単電子パスゲート回路<sup>46)</sup> やトンネル負荷回路<sup>47)</sup> を組み合わせると回路設計の自由 度が大きくなる。

これらの論理回路の動作は CMOS 回路と似ており、既存回路の概念を適用しやすく機能の設計が容易である。動作がスタティック論理なので使いやすい。しかし、CMOS 回路と異なって入出力の分離が弱い(回路動作が次段回路の影響を強く受ける)ので、多段回路の設計では注意を要する。

# 4.2.2 単電子注入形論理ゲート回路

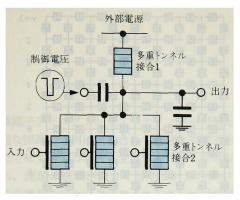

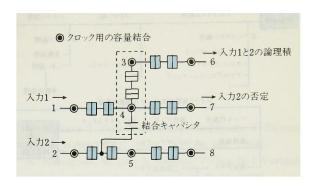

大規模回路を構成するためには、単位ゲート回路ごとに入出力の分離をつけて方向性を確保する必要がある。また素子パラメーターのバラツキに対して安定な方がよい。そこで多重トンネル接合とクロック駆動を組み合わせた単電子注入形論理ゲート回路⁴8)が提案された。その構成を図12に示す。単電子注入用の多重トンネル接合1と、動作の終状態を決める並列接続の多重トンネル接合2とからなる。制御電圧としてパルス電圧を印加することにより、単電子を外部電源から出力ノードに注入し、多重トンネル接合2の最も小さなクーロンブロッケード領域により終状態を決める。回路動作のためには多重トンネル接合に電圧増幅率が必要であり、大きい電圧増幅率を得る方法としてドレイン2重トンネル障壁構造³5)やドレイン空間電荷領域構造¹¹¹)が提案されている。

図 12 単電子注入型論理回路48).

図 13 位相制御論理回路.多層クロックで駆動.単電子があるときを論理 1,ないときを論理 0 とする.

図 14 二分決定グラフ論理回路. (a)4変数論理(AB+CD)を表す二分決定グラフ. (b)単電子による単位デバイス(二分岐スイッチ). (c)単位デバイスを組み合わせた論理回路. (d)動作シミュレーション結果. クロック $\phi$ 1- $\phi$ 3 は $\phi$ 0 の位相を 90 度づつ遅らせたもの. 出力電荷は電子電荷で正規化. 回路パラメーターは,トンネル抵抗 100 k $\Omega$ ,トンネル容量,入力結合容量,クロック容量いずれも 10 aF,動作温度 0 K.

# **4.2.3** 位相制御論理ゲート回路と二分決定グラフ論 理回路

以上に述べた一連の論理回路は(従来の Si 回路と同じく)入出力が電圧信号であり、そのため前段ゲートの出力電圧で次段ゲートの入力を駆動する構成をとっている。ところで、単電子現象の本質は電子を1つずつ制御して輸送できることなので、ゲート間の信号伝達を単電子の輸送そのもので行うことも可能である。この考え方を進めると、「単電子の輸送経路を切り換えることで論理を行う」という、真に単電子らしい回路構成に到達する。

一例が位相制御論理ゲート回路<sup>49)</sup> である。構成概念を 図13 に示す。多数の島ノードとそれらを結ぶトンネル接 合からなる。各島ノードに容量を介して多相クロック電圧 を印加し、単電子ポンプの原理で電子を一方向に移動させ る. いま入力 1 として電子をノード 1 から入れると、それはクロックに従って移動し、ノード 4 を経て 7 から流れ出る。このとき、もし入力 2 として別の電子がノード 2 から入っていれば、結合キャパシタを介した電子間の反発力のため、入力 1 の電子は単電子スイッチ(図の点線枠)の部分でノード 4 から 3 に移動してノード 6 から流れ出る。以上の動作によって AND 論理(ノード 6 でみる)や NOT論理(ノード 7 でみる)が得られる。この回路を利用して、2 次元 CCD 論理回路に類似した信号処理回路 $^{50}$  が考案されている。

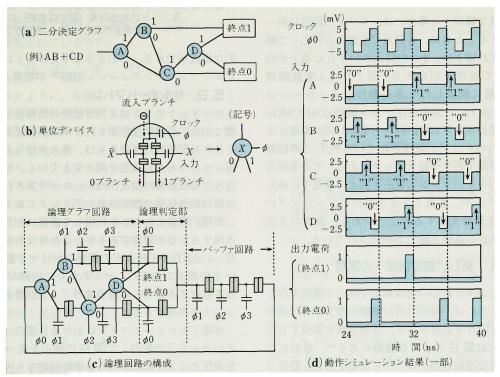

「電子の輸送経路による論理」を二分決定グラフと組み合わせた形の回路<sup>12)</sup>も提案されている。二分決定グラフとは、ブール代数式や真理値表とは異なる手法-有向グラフを使って論理を表現する方法である。この二分決定グラ

図 15 情報処理を実現するための各種プロセス54).

フを単電子回路で構成する場合には、グラフの経路に沿って電子を輸送するとともに、各節点で変数入力に応じて輸送経路を変更すればよい。2つの終点のいずれに電子が到達するかをみて論理を判定する。例として4変数論理AB+CDを回路に構成したときの動作シミュレーション51)を図14に示す。(二分決定グラフ論理はSi CMOS回路でも最近注目されており、パストランジスタ構成による高速・低電力のチップが試作されている522。)この回路の基本要素は単電子の2分岐スイッチである。その実現方法として、入力キャパシタから電圧を加えて単電子の流れを変える方法49.51)や、多重トンネル接合のクーロンブロッケード領域を直接変調する方法53)がある。後者の方法による2分岐動作の基礎実験53)が報告されている。

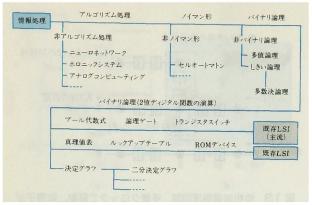

#### 5. 新しい論理機能への展開

単電子現象のような新しい物理現象を使って機能を作り出そうとするときには、現用主流の情報処理方法とは異なる方向にも目を向ける必要がある。情報処理を実現するためのプロセスには図15のような種類がある<sup>54)</sup>。最近になって、いろいろな情報処理プロセスと単電子現象を結びつける研究が行われるようになった。以下の例はすべて理論検討レベルであるが、今後の展開が期待される。各種の情報処理方法については文献54)にある参考文献を参照されたい

# 5.1 ニューロネットワーク

ニューロネットワークとは、重みつき結合(シナプス)を持つ多数のしきい素子(ニューロン)からなる並列分散形の情報処理システムである。パターン識別・予測と制御・最適化問題などに応用分野がある。

単電子ニューロネットワークの構成例が提案されている。単電子インバータのニューロンとキャパシタのシナプスを組み合わせ、ターンスタイルで蓄積電荷を制御して巧みに可変重みをつくる55)。極めてコンパクトかつ低電力の回路ができる。ところで、ニューロネットワークのうち相互結合形ネットワークと呼ばれる一群のものでは「いかにローカルミニマムを避けてエネルギー最小状態に収束させるか」ということが重要な問題である。解決方法の一つは各ニューロンを確率動作させることである。そこにトンネル現象の確率性を利用すれば、いかにも単電子らしい機能

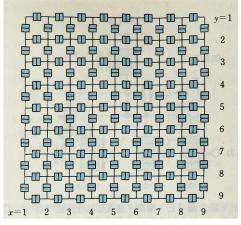

図16 島ノードの正方配列の例(9×9マトリックス)<sup>57</sup>。 各ノードの対地容量(図では省略)の大きさによっ てクーロン相互作用のしゃへい距離が決まる。

的な構成ができる。このような考えのもとに、単電子形の ボルツマンマシンニューロン回路<sup>56)</sup> が提案されている。

#### 5.2 セルオートマトン

セルオートマトンは並列分散形の情報処理システムの一種である。近接相互作用を行う単位演算要素(セル)をマトリクス配列した構造をもつ。各セルは与えられた相互作用ルールのもとで状態を刻々変えていく。役に立つ処理を行うために各種の相互作用ルールが考案されている。応用分野は画像処理や物理現象モデリングである。

単電子現象そのものを利用して直接に相互作用ルールを 実現することが理想であるが、これはなかなか難しい。た だし、AND や OR などの簡単なバイナリ論理については 1~2の提案がある<sup>13)</sup>。セルあたりの回路が大きくなるこ とを容認するなら、単電子論理ゲート回路を使えば多くの ルールが実現できる。

単電子セルオートマトンにおける目標の一つは,島ノードのセルを正方配列した図 16 の構造を使って有用な処理を実現することにある(この単純構造なら大規模なものを容易に製作できる)。この構造で得られる相互作用ルールは限られるが,しかし幾つかの面白い研究がある。たとえば,本構造に電子流を与えて非平衡状態におくと,条件によって電子分布のバンチングが発生する570。この現象はBZ(ベルーソフ=ジャボチンスキー)反応と呼ばれる特殊な化学反応で生じる「非平衡の解放系における安定と非安定の現象」と類似のものであり,画像処理やカオス生成などに応用の可能性をもつ。なお,BZ 反応の方はすでに応用研究が進んでいる。

# 5.3 アナログコンピューティング

アナログコンピューティングとは、数学の問題を適切な物理系の動作で相似して解く手法のことをいう(デジタルニアナログというときのアナログとは意味が異なる)。その例として、微分解析器(積分器を組み合わせた電子回路で微分方程式を解く)や張力演算器(石鹼膜パターンの平衡状態を利用して最小スタイナー木問題の近似解を得る)などが挙げられる。本質的に高速並列の演算である(実際には前処理と後処理が必要であるがここでは触れない)。

解こうとする問題を単電子系で相似できれば、それによ

って単電子アナログコンピューティングが可能となる。適用可能な問題の一例は組み合わせ最適化問題である。通常の解法ではすべての場合を全数チェックしなければならないから、問題の規模が大きくなると計算時間が膨大になる。この問題をアナログコンピューティングで解くときには、単電子の性質をうまく利用してその問題を相似するような系を構成し、その状態を観察して解を求める。3 彩色問題や充足可能性問題を解析する単電子アナログコンピューティングが提案されている58,59)。

## 6. む す び

以上述べてきたように、単電子デバイスの研究は、生まれながらにして従来の縦割型学問・技術体系を越えた総合分野としての性格をもっており、基礎物理から微細加工、デバイス、回路、情報処理にわたる幅広い領域で研究者を魅了する輝きをもっている。しかし、実用化への見通しを語ることはむずかしい。現在はまだ未成熟な段階であるが、いずれ SiLSI という巨象との比較論にさらされるからである。一方で、単電子デバイスは LSI が行き着く末、すなわち「微細化の果ての姿」を先取りして研究しているという側面もある。将来、単電子デバイスが LSI の一部を置き換え融合する、というステップを踏むことも考えられ、LSI との対立技術としての比較論に片寄ることなく幅広い視点から研究を推進する必要があると思われる。

#### 文 献

- 1) 単電子デバイスと物理に関する全般的な解説としては、次の文献を参照されたい。K. K. Likharev: IBM J. Res. Dev. 32, 144 (1988); D. V. Averin and K. K. Likharev: Quantum Effects in Small Disordered Systems, ed. B. L. Altshuler, P. A. Lee and R. A. Webb (Elsevier, Amsterdam, 1991); H. Grabert and M. H. Devoret, ed.: Single Charge Tunneling, NATO ASI Series (Plenum Press, New York, 1992).

- 2) 上田正仁:応用物理 62, 889 (1993).

- T. A. Fulton and G. J. Dolan: Phys. Rev. Lett. 59, 109 (1987).

- L. J. Geeligs, V. F. Anderegg, P. A. M. Holweg, J. E. Mooij, H. Pothier, D. Esteve, C. Urbina and M. H. Devoret: Phys. Rev. Lett. 64, 2691 (1990).

- H. Pothier, P. Lafarge, C. Urbina, D. Esteve and M. H. Devoret: Europhys. Lett. 17, 249 (1992).

- 6) 矢野和男,石井智之,橋本孝司,小林 孝,村井二三夫,関 浩一:応用物理 **63**,1248 (1994).

- Y. Takahashi, M. Nagase, H. Namatsu, K. Kurihara, K. Iwadate, Y. Nakajima, S. Horiguchi, K. Murase and M. Tabe: Electronics Letters, 35, 136 (1995); Y. Takahashi, H. Namatsu, K. Kurihara, K. Iwadate, M. Nagase and K. Murase: IEEE Trans. Electron Devices, 43, 1213 (1996).

- 8) H. Ishikuro, T. Fujii, T. Saraya, G. Hashiguchi, T. Hiramoto and T. Ikoma: Appl. Phys. Lett. 68, 3585 (1996).

- K. Matsumoto, M. Ishii, K. Segawa, Y. Oka, B. J. Vartanian and J. S. Harris: Appl. Phys. Lett. 68, 34 (1996).

- K. Nakazato, T. J. Thornton, J. White and H. Ahmed: Appl. Phys. Lett. 61, 3145 (1992).

- K. Nakazato and H. Ahmed: Appl. Phys. Lett. 66, 3170 (1995)

- N. Asahi, M. Akazawa and Y. Amemiya: IEEE Electron Devices ED-42, 1999 (1995).

- P. D. Tougaw, C. S. Lent and W. Porod: J. Appl. Phys. 74, 3558 (1993).

- 14) S. Tarucha, D. G. Austing, T. Honda, R. J. van der Hage and L. P. Kouwenhoven: Phys. Rev. Lett. 77, 3613 (1996).

- 15) 藤原 聡,高橋庸夫,村瀬克実:第57回応用物理学会学術講演会予稿集,p.67(1996).

- 16) H. Hasegawa: Int. Symp. Formation, Physics and Device Application of Quantum Dot Structures, Sapporo, November 1996; 葛西誠也, 橋詰 保, 長谷川英機:応用物理学会学術講演予稿集, p. 65 (1996).

- 17) T. Hiramoto, H. Ishikuro, T. Fujii, G. Hashiguchi and T. Ikoma: Int. Symp. Formation, Physics and Device Application of Quantum Dot Structures, Sapporo, November 1996; 石黒仁揮,藤井呂如,更屋拓哉,橋口 原,平本俊郎,生駒俊明:第57回応用物理学会学術講演会予稿集,p. 65 (1996).

- 18) C. J. Golter: Phisica 17, 777 (1951).

- 19) G. J. Dolan and J. H. Dunsmuir: Physica B 152, 7 (1988).

- 20) J. S. Tsai:応用物理 63, 1232 (1994).

- U. Meirev, M. A. Kastner and S. J. Wind: Phys. Rev. Lett. 65, 771 (1990).

- 22) M. A. Kastner: Physics Today, p. 24 (January, 1993).

- J. Weis, R. J. Haug, K. v. Klitzing and K. Ploog: Phys. Rev. Lett. 71, 4019 (1993).

- 24) K. Yano, T. Ishii, T. Sano, T. Mine, F. Murai and K. Seki: 1996 IEEE Int. Solid-State Circuits Conference, p. 266 (1996).

- S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe and K. Chan: Appl. Phys. Lett. 68, 1377 (1996).

- S. Oda, M. Kimura and M. Otobe: IEEE Silicon Nanoelectronics Workshop, Honolulu, June 1996.

- A. Fujiwara, Y. Takahashi, K. Murase and M. Tabe: Appl. Phys. Lett. 67, 2957 (1996).

- 28) K. Nakazato, R. J. Blaikie and H. Ahmed: J. Appl. Phys. 75, 5123 (1994).

- 29) G. Chen, G. Klimeck, S. Datta, G. Chen and W. A. Goddard III: Phys. Rev. **B 50**, 8305 (1994).

- 30) A. Ohata and A. Toriumi: Int. Conf. Solid State Materials and Devices, Ext. Abstracts, p. 455 (1996).

- 31) たとえば文献 1) のうち, 次のものを参照されたい。D. V. Averin and Yu. V. Nazarov: Single Charge Tunneling, ed.

- H. Grabert and M. Devoret, p. 217 (Plenum, New York, 1992)

- 32) Y. Takahashi, S. Horiguchi, A. Fujiwara and K. Murase: Physica B 227, 105 (1996).

- 33) T.-C. Chen, C. Wang, G.C. Abeln, J. R. Tucker, J. W. Lyding, Ph. Avouris and R. E. Walkup: Science, 268, 1590 (1995).

- 34) M. Tabe and T. Yamamoto: Appl. Phys. Lett. **69**, 2222 (1996); M. Tabe and T. Yamamoto: Surf. Sci. 印刷中.

- Y. Matsumoto, T. Hanajiri, T. Toyabe and T. Sugano: Jpn.

J. Appl. Phys. 35, 1126 (1996).

- M. Akazawa and Y. Amemiya: Jpn. J. Appl. Phys. 35, 3569 (1996).

- 37) 桑村信博,谷口研二,浜口智尋:電子情報通信学会論文誌 J77-C-II, p. 221 (1994).

- 38) T. A. Fulton, P. L. Gammel and L. N. Dunkleberger: Phys. Rev. Lett. 67, 3148 (1991).

- 39) P. Lafarge, P. Joyez, H. Pothier, A. Cleland, T. Holst, D. Esteve, C. Urbina and M. N. Devoret: C. R. Acad. Sci. Paris, t. 314, Serie II, 883 (1992).

- K. Nakazato, R. J. Blaikie, J. R. A. Cleaver and H. Ahmed: Electron. Lett. 29, 384 (1993).

- 41) P. D. Dresselhaus, L. Ji, S. Han, J. E. Lukens and K. K. Likharev: Phys. Rev. Lett. 72, 3226 (1994).

- 42) K. Yano, T. Ishii, T. Hashimoto, T. Kobayashi, F. Murai and K. Seki: IEEE Trans. Electron Devices **ED-41**, 1628 (1994).

- 43) K. K. Likharev: Mikroelektronika 16, 195 (1987).

- 44) Yu. V. Nazarov and S. V. Vyshenskii: Single-Electron Tunneling and Mesoscopic Devices, ed. H. Koch and H. Lubbig, p. 61 (Springer-Verlag, Berlin, 1992).

- 45) J. R. Tucker: J. Appl. Phys. 72, 4399 (1992).

- 46) 谷口研二,桐原正治:1996年電子情報通信学会エレクトロニ クスソサイアティ大会講演論文集 2 p. 249 (1996).

- H. Fukui, M. Fujishima and K. Hoh: Jpn. J. Appl. Phys. 34, 1345 (1995).

- 48) K. Nakazato: 14th Symp. Future Electron Devices, October, 1995.

- 49) K. Nakazato and J. White: Tech. Dig. Int. Electron Device Meeting, p. 487 (1993).

- 50) M. G. Ancona: J. Appl. Phys. 79, 526 (1996).

- 51) 朝日 昇,赤澤正道,雨宮好仁:第57回応用物理学会学術講演会予稿集,p. 72 (1996).

- 52) K. Yano, Y. Sasaki, K. Rikino and K. Seki: IEEE J. Solid-State Circuits 31, 792 (1996).

- K. Nakazato: 54th Annual Device Research Conf. Dig., p. 180 (1996).

- 54) 雨宮好仁, 赤澤正道:応用物理 64, 765 (1995).

- 55) M. Kirihara and K. Taniguchi: Int. Symp. Formation, Physics and Device Application of Quantum Dot Structures, Sapporo, November 1996; 桐原正治, 谷口研二:第57回応用物理学会学術講演会予稿集, p. 68 (1996).

- 56) N. Akazawa and Y. Amemiya: Appl. Phys. Lett. **70**, No. 5 (1997); 赤澤正道, 雨宮好仁:第 57 回応用物理学会学術講演会予稿集, p. 72 (1996).

- 57) M. Tabe, N. Asahi, Y. Amemiya and Y. Terao: Int. Symp. Formation, Physics and Device Application of Quantum Dot Structures, Sapporo, November 1996; 田部道晴,朝日 昇,雨宫好仁:第57回応用物理学会学術講演会予稿集, p. 62 (1996).

- 58) Y. Amemiya: IEICE Trans. Electronics, E79-C, 1481 (1996).

- 59) 赤澤正道,雨宮好仁:第57回応用物理学会学術講演会予稿集, p. 70 (1996).

(1996年10月18日 受理)